为什么医院控制耗占比【硬件-笔试面试题-67】硬件/电子工程师,笔试面试题(知识点:DCDC开关电源电路的损耗,开关损耗,导通损耗,电感损耗)

目录

1、题目

2、解答

一、功率器件损耗(最主要损耗来源)

1. MOS 管损耗(开关管 / 同步整流管)

(1)导通损耗(Conduction Loss, (P_{cond})):电流流过时产生(I^2R)损耗

(2)开关损耗(Switching Loss, (P_{sw})):电压与电流存在交叠区

(3)驱动损耗(Gate Drive Loss, (P_{gate})):充放电电流流过驱动电阻(R_g)产生损耗

2. 二极管损耗(续流 / 整流二极管):耗主要来自正向导通损耗和反向恢复损耗

(1)正向导通损耗(Forward Conduction Loss, (P_{D,cond}))

(2)反向恢复损耗(Reverse Recovery Loss, (P_{D,rr}))

二、无源器件损耗

1. 电感损耗(Inductor Loss):铜损与铁损

(1)铜损(Copper Loss, (P_{L,cu}))

(2)铁损(Core Loss, (P_{L,core}))

2. 电容损耗(Capacitor Loss)

(1)ESR 损耗(ESR Loss, (P_{C,esr}))

(2)ESL 损耗(ESL Loss, (P_{C,esl}))

3. 电阻损耗(Resistor Loss)

三、控制电路损耗(Control Circuit Loss)

四、损耗分布与效率优化方向

总结

题目汇总版--链接:

【硬件-笔试面试题】硬件/电子工程师,笔试面试题汇总版,持续更新学习,加油!!!-CSDN博客

【硬件-笔试面试题-67】硬件/电子工程师,笔试面试题(知识点:DCDC开关电源电路的损耗,开关损耗,导通损耗,电感损耗)

讲讲开关电源中有哪些损耗

小米笔试题

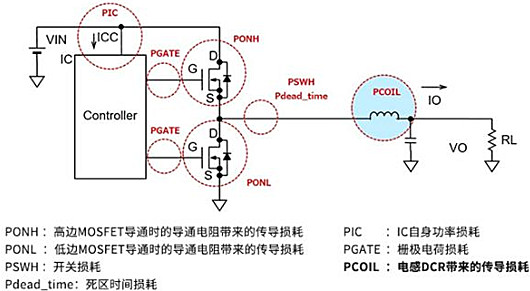

DC-DC 电源在能量转换过程中必然存在损耗,这些损耗不仅降低电源效率,还会转化为热量导致器件发热,甚至影响可靠性。损耗的核心来源可分为功率器件损耗(占比最高)、无源器件损耗、控制与驱动损耗三大类,具体分类及计算逻辑如下:

一、功率器件损耗(最主要损耗来源)

功率器件(MOS 管、二极管、同步整流 MOS 管)直接承担能量的 “开关” 与 “续流” 功能,承受高电压、大电流,其损耗占总损耗的 60%~90%,主要包括导通损耗、开关损耗、反向恢复损耗三类。

1. MOS 管损耗(开关管 / 同步整流管)

MOS 管是 DC-DC 的核心开关器件,损耗与导通电阻、开关速度、驱动条件直接相关。

(1)导通损耗(Conduction Loss, (P_{cond})):电流流过时产生(I^2R)损耗

- 产生原因:MOS 管导通时,漏源极间存在导通电阻(R_{ds(on)}),电流流过时产生(I^2R)损耗;若存在体二极管导通(如同步整流续流阶段),还会产生二极管正向损耗。

- 适用场景:MOS 管处于 “完全导通” 的稳态阶段(占空比D对应的时间内)。

- 计算逻辑:

- 对于连续导通模式(CCM)的降压型(Buck)拓扑,假设电流纹波较小(近似恒定电流(I_{avg})):(P_{cond} = D imes I_{avg}^2 imes R_{ds(on)}) (D为占空比,(I_{avg})为 MOS 管平均导通电流,(R_{ds(on)})需考虑实际结温下的阻值 —— 温度升高时(R_{ds(on)})会增大,通常需乘以 1.5~2 倍的温度系数)

- 若电流纹波较大(如电感较小),需用有效值电流(I_{rms}) 计算(更准确):(P_{cond} = I_{rms}^2 imes R_{ds(on)}) (CCM 模式下,(I_{rms} = sqrt{I_{avg}^2 + (Delta I_L/2sqrt{3})^2}),(Delta I_L)为电感电流纹波)

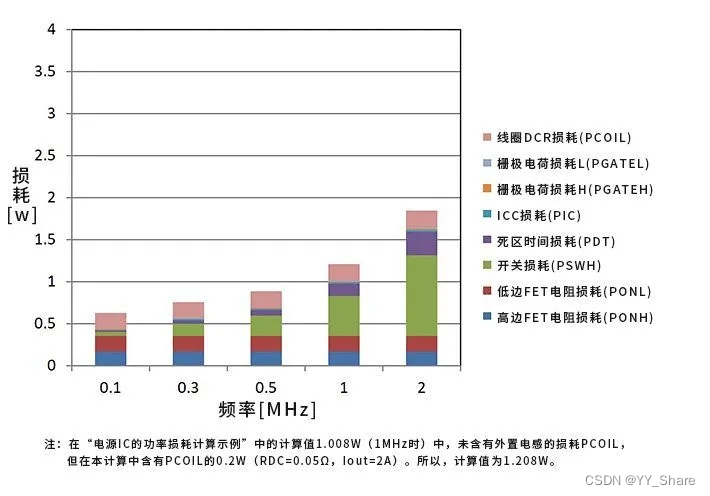

(2)开关损耗(Switching Loss, (P_{sw})):电压与电流存在交叠区

- 产生原因:MOS 管从 “关断→导通”(开通损耗(P_{sw,on}))或 “导通→关断”(关断损耗(P_{sw,off}))的过渡阶段,电压与电流存在交叠区(即电压未降到 0 时电流已上升,或电流未降到 0 时电压已上升),交叠区的瞬时功率积分即为开关损耗。

- 关键影响因素:

- 开关频率(f_s):频率越高,单位时间内开关次数越多,总开关损耗越大(成正比);

- 驱动能力:驱动电流不足会延长开关过渡时间,增大交叠区;

- 寄生参数:漏源极寄生电容(C_{oss})、线路寄生电感(产生电压尖峰)会增加关断损耗。

- 计算逻辑(近似简化,适用于硬开关拓扑): 假设开关过渡时间内电压从(V_{in})(输入电压)线性变化到 0,电流从 0 线性变化到(I_{peak})(峰值电流),则单次开关损耗为:(P_{sw,single} = frac{1}{2} imes V_{in} imes I_{peak} imes t_{overlap}) ((t_{overlap})为电压 - 电流交叠时间) 总开关损耗(开通 + 关断):(P_{sw} = f_s imes (P_{sw,on,single} + P_{sw,off,single})) (软开关拓扑如 LLC、ZVS 可大幅减小开关损耗,交叠区近似为 0)

(3)驱动损耗(Gate Drive Loss, (P_{gate})):充放电电流流过驱动电阻(R_g)产生损耗

- 产生原因:驱动电路需为 MOS 管栅源极电容(C_{iss})(输入电容)充放电 —— 导通时充电,关断时放电,充放电电流流过驱动电阻(R_g)产生损耗;同时,栅极与漏极间的密勒电容(C_{gd})会在开关过渡阶段产生额外的驱动电流。

- 计算逻辑: 每次开关需充放电的总电荷为(Q_g)(MOS 管栅极总电荷, datasheet 参数),则单次驱动损耗为(V_{gs} imes Q_g)((V_{gs})为栅极驱动电压,通常 10~15V),总驱动损耗:(P_{gate} = f_s imes V_{gs} imes Q_g) (驱动电阻(R_g)增大时,充放电时间延长,会间接增大开关损耗,但驱动损耗本身变化不大)

2. 二极管损耗(续流 / 整流二极管):耗主要来自正向导通损耗和反向恢复损耗

传统非同步 DC-DC(如 Buck)中,续流二极管是关键器件,损耗主要来自正向导通损耗和反向恢复损耗。

(1)正向导通损耗(Forward Conduction Loss, (P_{D,cond}))

- 产生原因:二极管导通时存在固定正向压降(V_{F})(硅管约 0.7V,肖特基管约 0.3V),电流流过时产生(V_F imes I)损耗。

- 计算逻辑(CCM 模式): 二极管导通时间对应占空比(1-D)(Buck 拓扑中,MOS 管关断时二极管续流),平均续流电流为(I_{avg}),则:(P_{D,cond} = (1-D) imes V_F imes I_{avg})

(2)反向恢复损耗(Reverse Recovery Loss, (P_{D,rr}))

- 产生原因:二极管从导通转为关断时,存储在 PN 结中的载流子需要时间释放,导致反向电流(I_{rr})(反向恢复电流)在反向电压(V_{R})(通常为输入电压(V_{in}))下流动,产生瞬时功率损耗。

- 关键影响因素:高频场景下((f_s>100kHz))反向恢复损耗显著增大;肖特基二极管因无 PN 结载流子存储,反向恢复损耗近似为 0(故高频 DC-DC 常用肖特基管)。

- 计算逻辑: 单次反向恢复损耗为(frac{1}{2} imes V_R imes I_{rr} imes t_{rr})((t_{rr})为反向恢复时间,datasheet 参数),总损耗:(P_{D,rr} = f_s imes frac{1}{2} imes V_R imes I_{rr} imes t_{rr})

二、无源器件损耗

无源器件(电感、电容、电阻)虽不直接参与开关动作,但存在寄生参数和能量损耗,占总损耗的 10%~30%。

1. 电感损耗(Inductor Loss):

电感是能量存储与传递的核心,损耗分为铜损(导线损耗)和铁损(磁芯损耗),高频下铁损可能超过铜损。

(1)铜损(Copper Loss, (P_{L,cu}))

- 产生原因:电感线圈导线存在直流电阻(R_{dc}),电流流过时产生(I^2R)损耗;高频下因趋肤效应(电流集中在导线表面),导线等效电阻(R_{ac})增大,额外产生交流铜损。

- 计算逻辑: 直流铜损:(P_{L,cu,dc} = I_{rms}^2 imes R_{dc})((I_{rms})为电感电流有效值); 交流铜损:需考虑趋肤效应系数(K_{skin})(频率越高,(K_{skin})越大,通常(K_{skin}=1.2~3)),则(P_{L,cu,ac} = I_{rms}^2 imes (R_{ac} - R_{dc})); 总铜损:(P_{L,cu} = I_{rms}^2 imes R_{ac})。

(2)铁损(Core Loss, (P_{L,core}))

- 产生原因:磁芯在交变磁场中因磁滞效应(磁畴反复翻转消耗能量)和涡流效应(磁芯中感应电流产生(I^2R)损耗)产生的损耗,与开关频率(f_s)、磁芯磁通密度变化量(Delta B)直接相关。

- 计算逻辑(常用经验公式,Steinmetz 方程):(P_{L,core} = K imes f_s^alpha imes Delta B^beta imes V_{core}) (K、(alpha)、(beta)为磁芯材料参数,datasheet 提供;(V_{core})为磁芯体积;(Delta B)为磁芯磁通密度变化量,由电感电流纹波(Delta I_L)和电感参数计算:(Delta B = frac{Delta I_L imes L}{N imes A_e}),N为匝数,(A_e)为磁芯有效截面积)

2. 电容损耗(Capacitor Loss)

输入 / 输出滤波电容、补偿电容的损耗主要来自等效串联电阻(ESR)损耗和等效串联电感(ESL)损耗,高频下 ESR 损耗占主导。

(1)ESR 损耗(ESR Loss, (P_{C,esr}))

- 产生原因:电容的电极电阻、电解质电阻等寄生电阻总和为 ESR,电流纹波(Delta I_C)流过 ESR 时产生(I^2 imes ESR)损耗。

- 计算逻辑: 电容电流纹波有效值为(I_{C,rms})(输入电容纹波与拓扑相关,如 Buck 输入电容纹波(I_{C,rms} = I_{avg} imes sqrt{D imes (1-D)})),则:(P_{C,esr} = I_{C,rms}^2 imes ESR) (电解电容 ESR 较大,高频下需并联陶瓷电容降低总 ESR)

(2)ESL 损耗(ESL Loss, (P_{C,esl}))

- 产生原因:电容引线、电极结构形成的寄生电感 ESL,高频下会产生(I^2 imes (2pi f_s imes ESL)^2)损耗,但通常远小于 ESR 损耗,仅在极高频率((f_s>1MHz))下需考虑。

3. 电阻损耗(Resistor Loss)

电流采样电阻、电压分压电阻、驱动电阻等的损耗为纯欧姆损耗,计算简单但不可忽视:

- 采样电阻损耗:电流采样电阻(R_s)流过采样电流(I_{sense}),损耗(P_{R,sense} = I_{sense,rms}^2 imes R_s);

- 分压电阻损耗:电压反馈分压电阻(R1/R2)流过静态电流(I_{div}),损耗(P_{R,div} = frac{V_{out}^2}{R1+R2})((V_{out})为输出电压);

- 驱动电阻损耗已归入 MOS 管驱动损耗,此处不再重复。

三、控制电路损耗(Control Circuit Loss)

控制芯片(PWM 控制器)、基准电压源、保护电路等的静态功耗,占总损耗的 5% 以下(低功率 DC-DC 中占比略高)。

- 静态电流损耗:控制芯片的供电电流(I_{CC})(datasheet 参数,通常几十 μA 到几 mA)流过供电电压(V_{CC}),损耗(P_{ctrl} = V_{CC} imes I_{CC});

- 基准源损耗:基准电压源(如 TL431)的静态电流(I_{ref})产生的损耗(P_{ref} = V_{ref} imes I_{ref});

- 这类损耗为 “固定损耗”,与负载电流无关,轻载时占总损耗比例会升高(如负载电流趋近于 0 时,控制电路损耗可能成为主要损耗)。

四、损耗分布与效率优化方向

不同拓扑、功率等级的 DC-DC 损耗分布差异较大,典型规律及优化方向如下:

总结

DC-DC 电源的总损耗为上述所有损耗之和,即:(P_{total} = P_{MOS} + P_{Diode} + P_{Inductor} + P_{Capacitor} + P_{Resistor} + P_{Control}) 电源效率(eta = frac{P_{out}}{P_{out} + P_{total}} imes 100%)((P_{out})为输出功率)。设计时需根据拓扑、功率、频率需求,针对性优化占比最高的损耗类型,才能实现高效、低发热的 DC-DC 电源。

题目汇总--链接:

【硬件-笔试面试题】硬件/电子工程师,笔试面试题汇总版,持续更新学习,加油!!!-CSDN博客