ultraflex怎么测试芯片半导体测试与ATE系统

目录

第一章 半导体测试与ATE系统

一、半导体测试基本概念

测试的基本概念

测试类型

CP

FT

SLT

Char

HTOL

EVB

二、ATE系统

自动化测试设备

93k

整体架构

PMU

Pin Electronics

三、ATE常规硬件介绍

LB/PC

Socket

ChangeKit

Hander

Prober

四、引用及参考:

测试的基本概念

测试:指将一定的激励信号加载到需要检测的半导体产品的输入引脚,然后在输出引脚检测电路的响应,并将它与期望的响应相比较以判断电路是否有故障的过程;

测试的正确性和有效性对产品的品质影响极大,当一颗芯片没有通过测试,则一定有fail的原因,可能是(1)测试本身存在错误;(2)制造加工过程存在问题;(3)设计存在缺陷;(4)产品规范有问题;测试的作用是检验芯片是否存在问题,诊断并确认是什么方面出现了问题,以及如何迭代修正它;

测试类型

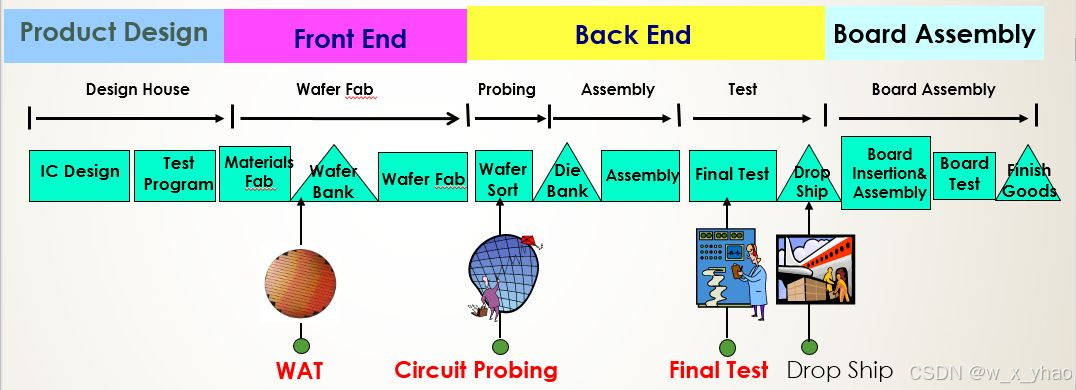

半导体测根据测试阶段和设备的不同大体上可以分为CP(Chip Probing / Circuit Probing)测试、FT(Final Test)、SLT(System Level Test)、EVB(Evaluation Board)测试;

ATE(Auto Test Equipment)测试通常指的是基于ATE机台进行的测试,在量产过程中通过ATE测试保证芯片出货的品质;如下图,ATE测试指在测试工厂进行,对量产芯片进行自动化测试,包含CP测试和FT测试;

注:

晶圆接收测试:(Wafer Acceptance Test, WAT)指在晶圆加工过程中进行的测试,通过WAT,晶圆厂可以早期识别晶圆加工中的问题,如掺杂浓度不一致、光刻问题或蚀刻缺陷等,从而及时调整生产过程,避免大规模生产不良产品。

CP

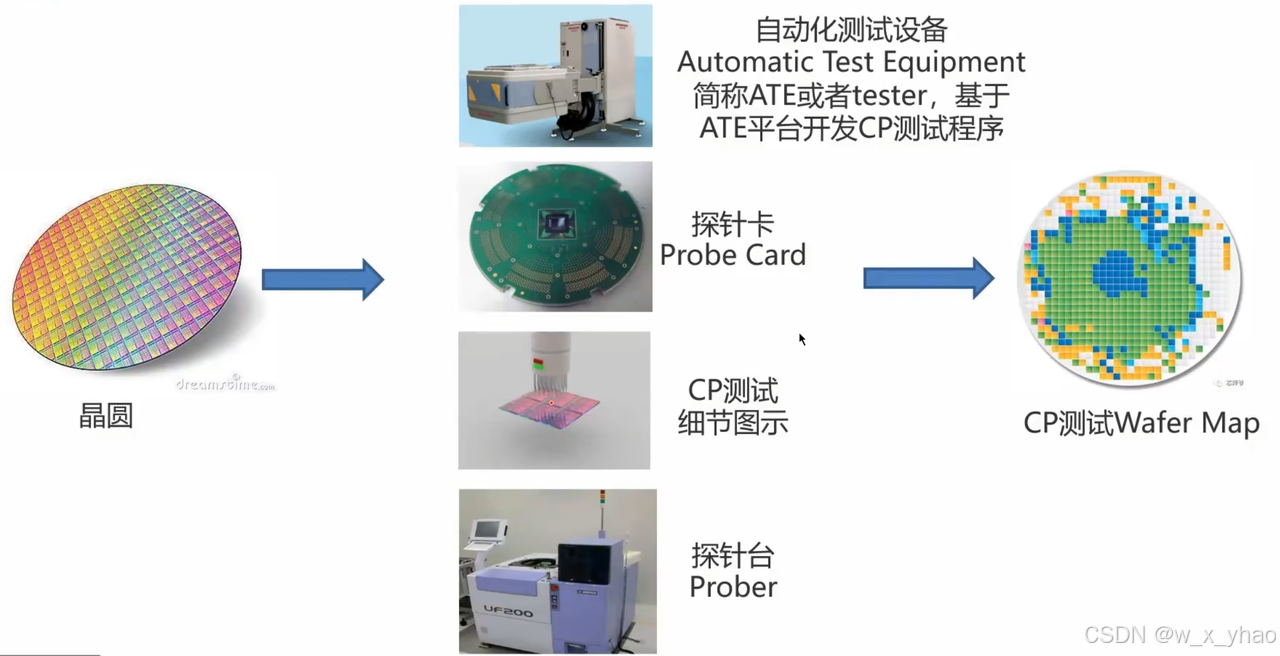

基本概念:CP测试位于晶圆制造之后,切割封装之前,在完整的晶圆上,通过探针与裸露的芯片管脚(bump)与测试机相连,对芯片的部分参数进行测试;

测试硬件需求:ProbeCard、ATE机台以及Prober;

主要目的:对晶圆的die电性能参数进行测试,保证生产质量和合格率,提升良率,降低后续封测成本;其次,由于封装时将芯片管脚封在内部,导致部分功能无法测试,因此只能在CP测试阶段进行;

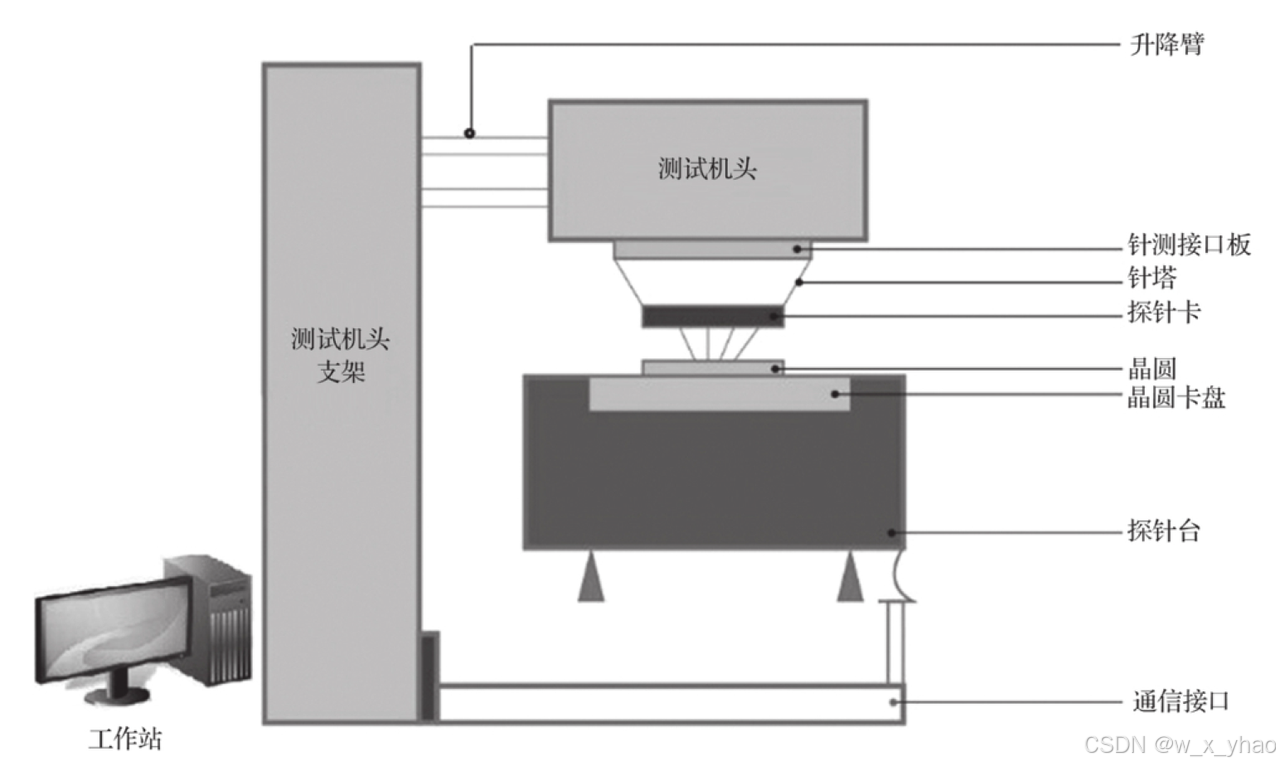

测试流程:如下图,在CP测试过程中主要使用的设备为prober和ATE测试机台。探针台的主要作用是承载晶圆,并不断移送DUT,使得探针卡上的探针可以和芯片管脚链接。由测试机对芯片施加激励信号并采集输出响应,判断芯片pass和fail。probe根据测试机的测试结果对打点标记,生成Wafer Map;

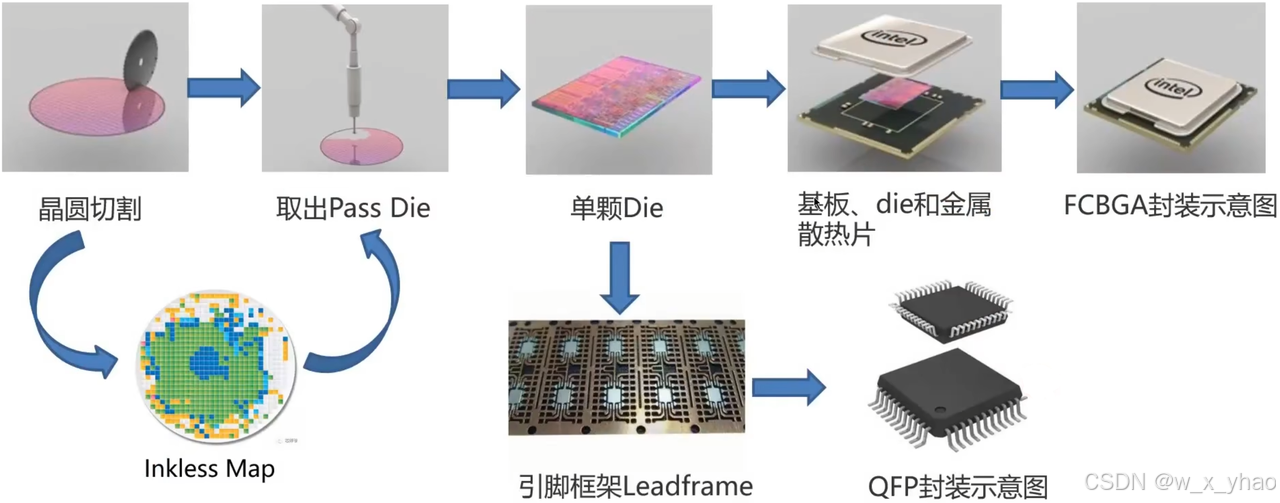

如下图,封装厂会根据Wafer Map对CP测试后的晶圆进行切割,取出标记pass的die,然后经过一系列操作后封装成成品芯片;

FT

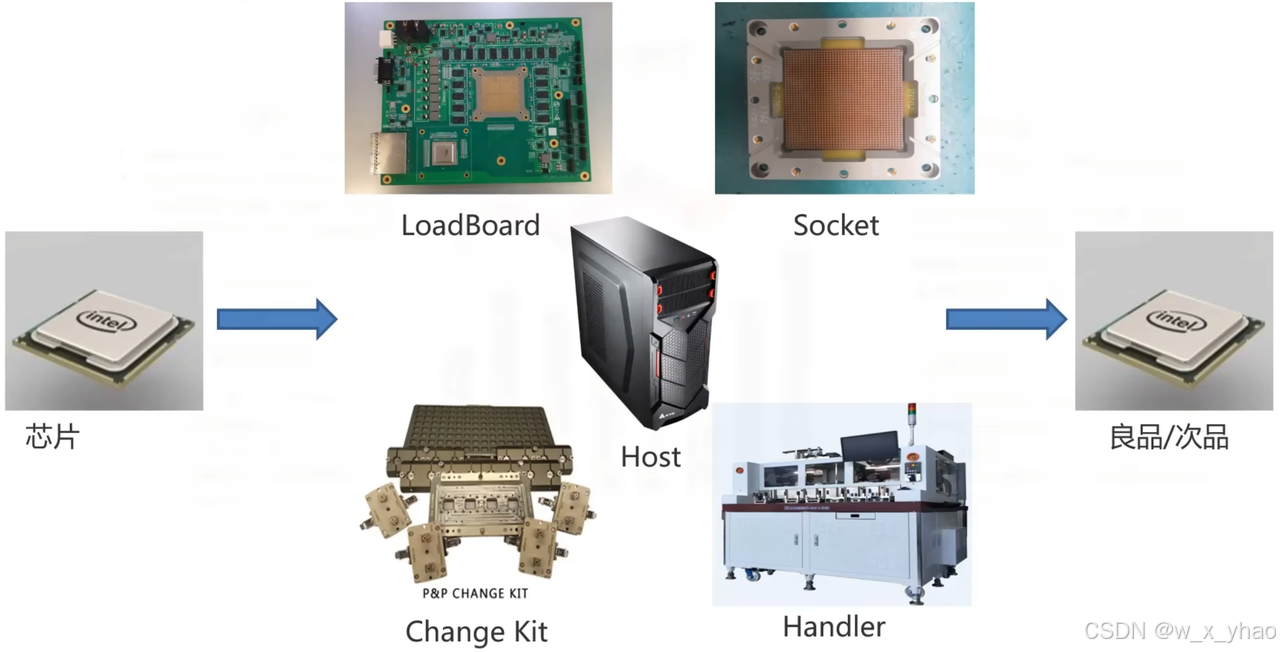

基本概念:FT测试位于芯片封装之后,在成品形态芯片上,通过探针与成品芯片管脚(ball)与测试机相连,对芯片的部分参数进行测试;

测试硬件需求:LoadBoard、Socket、ATE机台、Handler以及ChangeKit;

主要目的:保证出厂的每颗芯片的功能和性能指标能够达到设计规范要求;

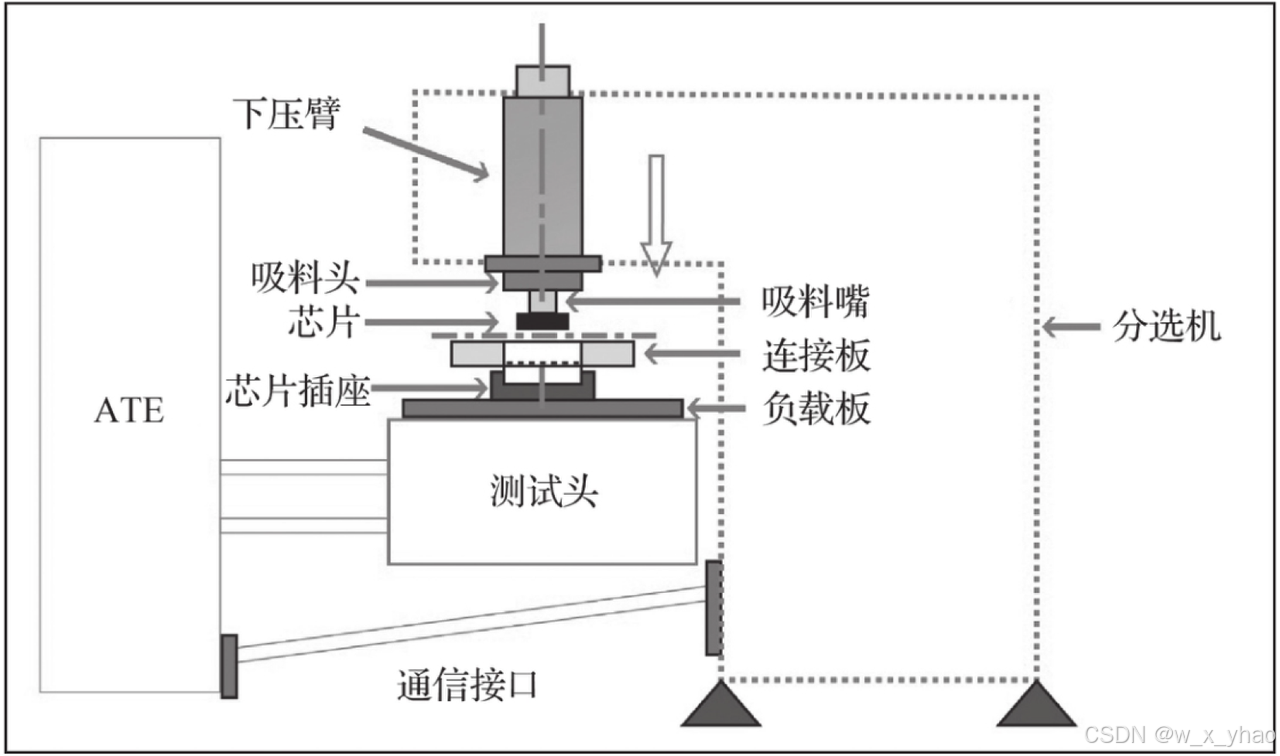

测试流程:如下图,在FT测试过程中主要使用的设备为Handler和ATE测试机台。Handler的主要作用是与ATE机台协同工作,通过机械臂和气嘴对芯片进行预热、移送,并为芯片提供下压力,使芯片的ball与LB上的探针紧密连接。由测试机对芯片施加激励信号并采集输出响应,判断芯片pass和fail。Handler根据测试机的测试结果对芯片进行分bin处理;

SLT

基本概念:SLT测试位于ATE测试后面,执行系统软件程序,测试芯片各个模块的功能是否正常。内容上通常包括芯片功能测试、高速接口测试以及DDR内存相关的测试等。

测试硬件需求:SLT测试板、Socket、Handler、ChangeKit以及测试主机与连接线等;

(注:SLT测试属于定制化测试,软件部分灵活度比较高,不需要基于自动化测试平台开发,完全由测试工程师自主开发。)

主要目的:验证具体模块的功能是否正常;

测试流程:如下图,在SLT测试过程中主要使用的设备为Handler和测试主机;具体测试流程同FT测试;

Char

基本概念:Char测试是一种对芯片全方位的检验,经常会对测试指标进行全工艺、全电压、全温度(PVT, Process, Voltage, Temperature)甚至是更多维度(如封装打线等)条件进行遍历。后文所提到的Shmoo、Vmin也是Char测试的一种体现;

主要目的:通过芯片在各个条件下测试结果的趋势,验证芯片设计的正确性,确保芯片达到设计规格,以及确定工艺窗口以及ATE测试的Spec。

测试流程:在Char测试中主要使用的设备为ATE测试机台、温控。温控的主要作用是拉偏环境温度,为芯片的测试提供一个高低温环境;ATE机台对芯片输入电源进行拉偏,以验证不同工艺角下芯片的性能;

HTOL

基本概念:老化测试(High Temperture Operating Life, HTOL)使评估芯片可靠性的一项关键性测试,主要通过高温激活失效机制来评估芯片寿命和长期通电运作的可靠性、稳定性;

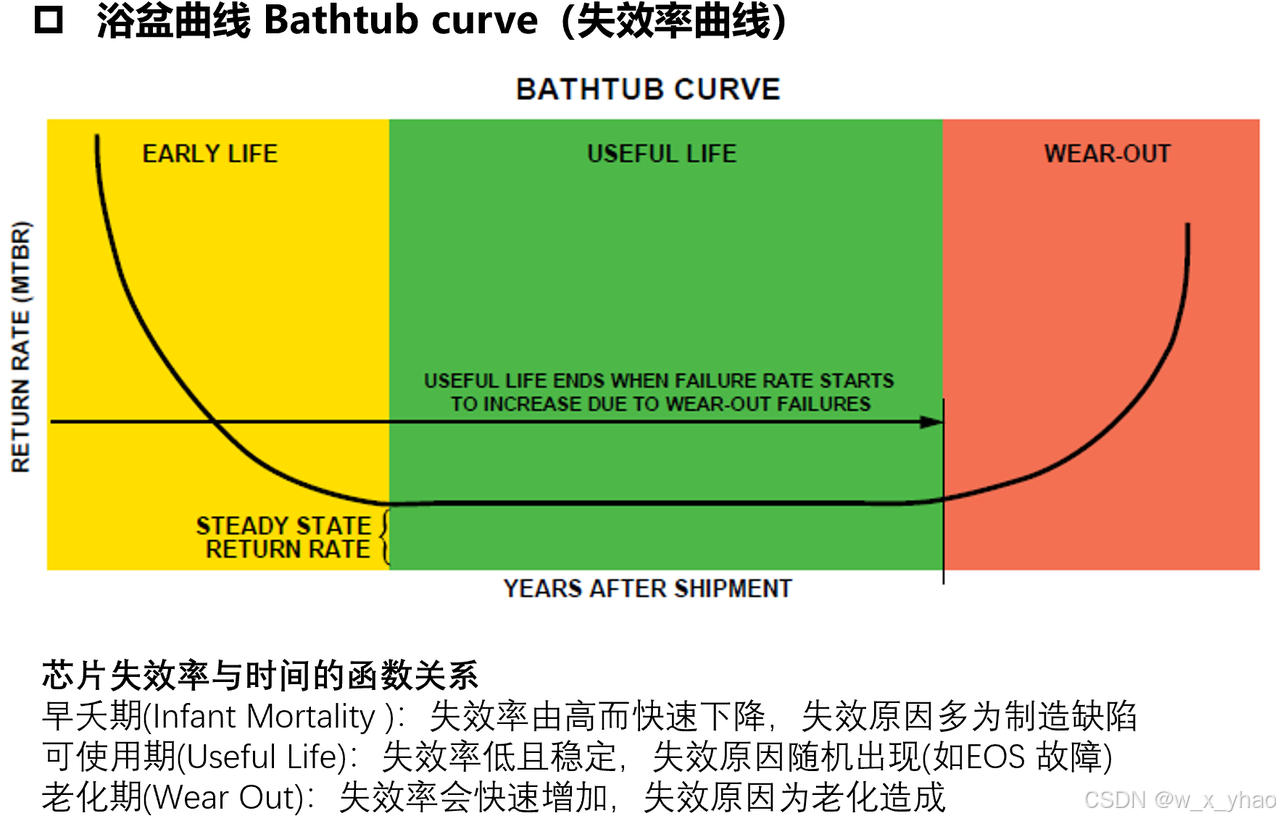

主要目的:根据浴盆曲线筛出早夭芯片,以及评估芯片寿命和长期上电运行所引起的电性能参数退化;

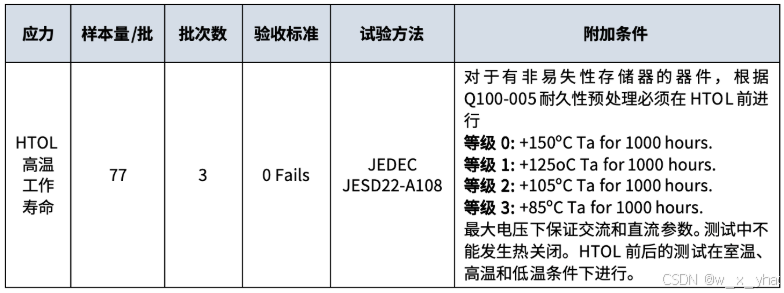

测试流程:HTOL测试涉及的主要设备和器件为HTOL设备、老化板、Socket。HTOL测试的主要实验参数是温度、电压和时间。试验温度是根据芯片的运行温度等级选择的,试验电压一般为芯片的最高工作电压、试验时间一般为1000小时;测试样品需要从不连续的三个批次中抽取,每个批次至少77颗样品,正式量产后也会选择性的抽样测试;在HTOL测试中HTOL设备会在线实时监控HTOL测试中每颗芯片的电压、电流、寄存器数据、时间及频率等诸多参数。在要求点(如0Hrs、168Hrs、500Hrs、1000Hrs)用ATE进行回测,确定芯片是否还正常工作,记录并分析老化过程中关键参数的变化,针对实验结果计算出芯片的失效率和平均失效时间;

EVB

基本概念:软件/驱动开发人员使用EVB开发板验证芯片的正确性,进行软件应用开发。

自动化测试设备

93k

业界用于SoC产品测试的ATE测试机台主要由两家提供:

-

Teradyne:J750 (low cost) and UltraFlex (high performance)

-

Advantest: V93000 and T2000

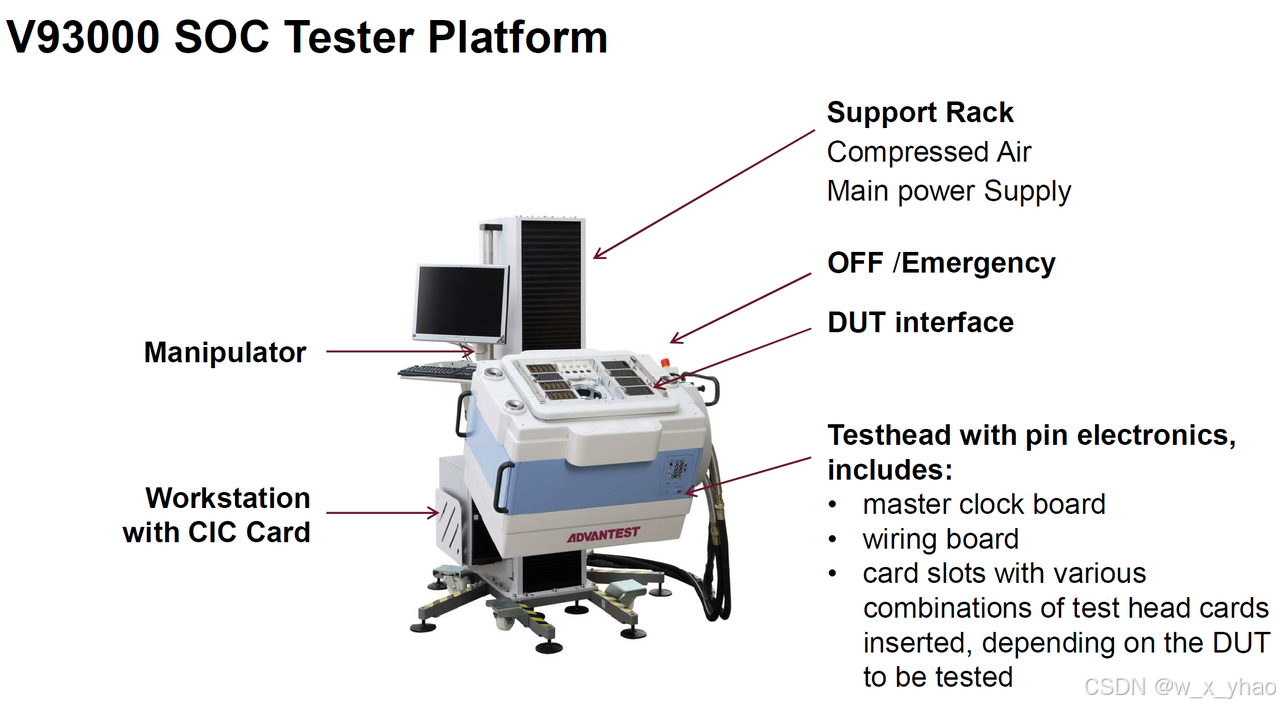

如下图,93k作为爱德万公司的高端测试设备,在结构上主要包含控制台、测试头(集成了供电、数字、模拟、射频等各类型的测试资源板卡)以及支撑架三大部分;

Manipulator机械手让测试头保持平衡状态,并且可以让测试头保持在任何所需要的位置,比如将测试头垂直或水平方向移动,旋转;

工作站:用来运行SmartTest软件,工作站中还包括与测试机进行数据通信的CIC卡;

支撑架:提供了用于测试系统运作的各种服务的连接,比如压缩空气,主系统电源;

红色的紧急关闭按钮可立即切断主电源;

DUT Interface:由高性能同轴电缆和pogo pins组成,可在测试头和测试板之间提供电气连接;

测试头:93k测试机的核心,集成了供电、数字、模拟、射频板卡,通过cable引出到DUT interface区域,所有板卡资源通过pogo pin与测试板建立电气连接;

整体架构

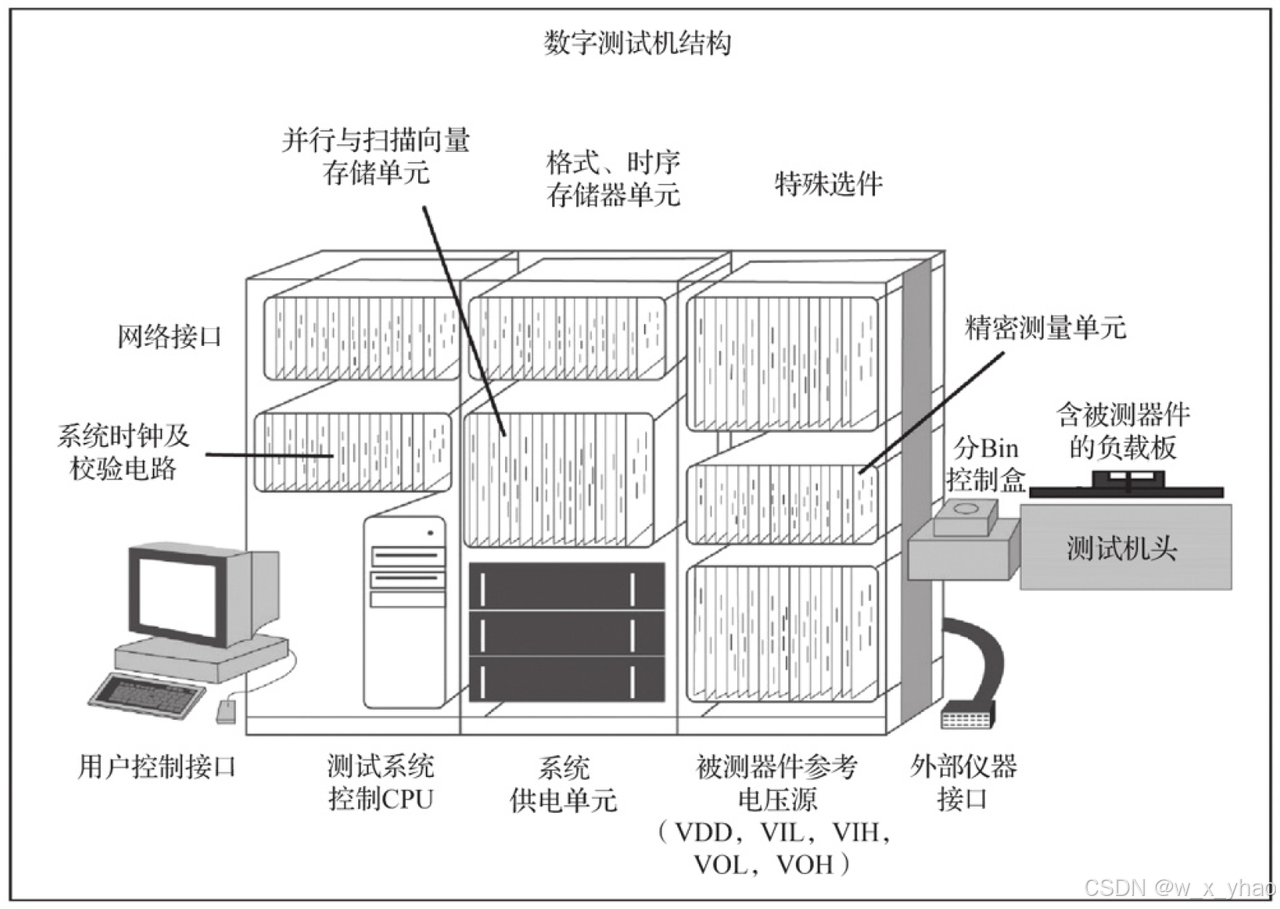

下图展示了一个混合信号测试机系统结构,包含了测量系统CPU、系统供电单元、PE电路、精密测量单元、向量存储单元、系统时钟等等;

测量系统控制CPU是系统的控制中心,它主要由控制测试系统的计算机组成。测试系统提供网络接口(Network Interface)用以传输测试数据;用户控制接口中的计算机的内存用来存储本地数据,显示器和键盘提供了测试操作员和测试系统的接口。

系统供电单元(System Power Supply,SPS),负责为测试系统供电。

PE(Pin Electronics)电路通常放置在测试头中,为待测期间提供输入信号并接收器件的输出信号,后面会详细介绍;

精密测量单元(Precision Measurement Uint, PMU),用于进行精确的DC参数测试,能够为DUT提供电流,测试电压;或提供电压,测量电流;后面会展开详细介绍;

并行与扫描向量存储单元(Parallel and Scan Vector Memory),用于存储测试向量,测试向量中描述了DUT的激励信号好响应信号。测试系统从向量存储单元中读取输入信号的输入状态作为激励信号,通过测试机的PE电路施加给DUT的响应引脚;再从DUT的输出引脚获取响应的输出信号,与测试向量中的响应的期待响应进行比较。

格式和时序存储单元(Format and Timing Storage Uint),存储了功能测试所需要的格式和时序设置等数据信息,信号格式和信号沿定义了输入信号的格式、上升沿、下降沿和采样点。时序单元从向量存储单元中接收激励状态,结合时序和信号格式信息,生成格式化的数据信号送给PE电路,进而施加给待测芯片;

外部仪器接口(Eleternal Instrument Interface),用于连接ATE和Handler,进行测试通信;

特殊选件(Special Tester Option),包含了一些选配的特殊功能,比如存储器测试、模拟电路测试所需要的特殊硬件结构;

系统时钟(Test System Clock),为测试系统提供同步时钟信号;

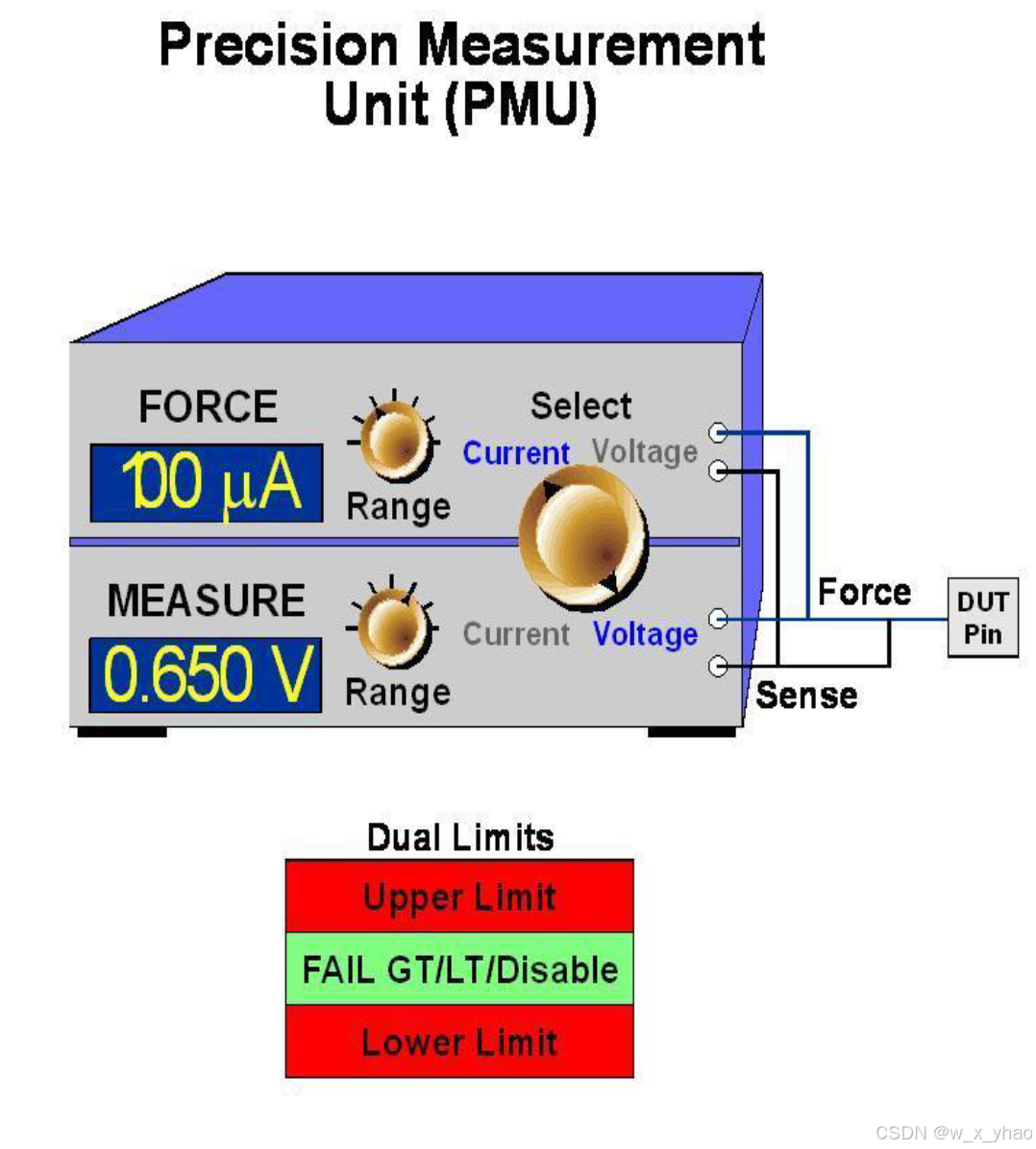

PMU

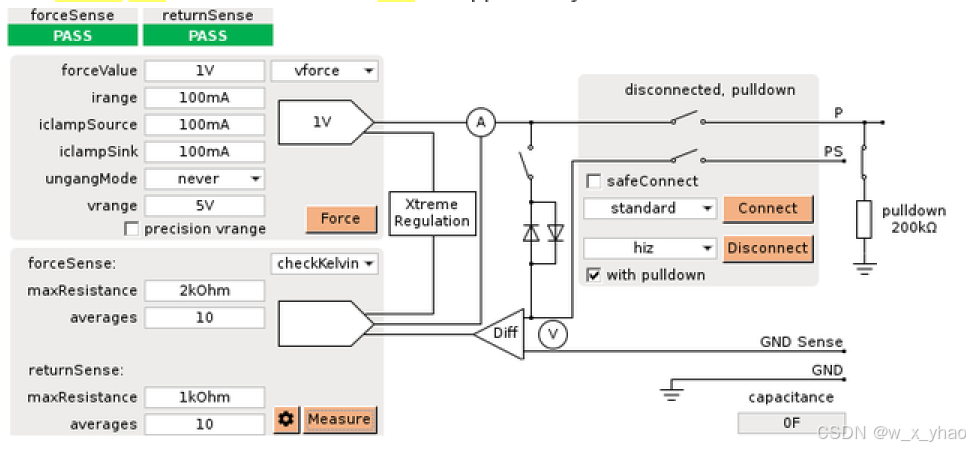

精密测量单元(Precision Measurement Uint, PMU)用于精确的DC参数测量,能够对DUT force电流meas电压或force电压meas电流;

-

Force and measurement modes 在对PMU进行编程时,force功能可选择force电压,meas电流;或force电流,meas电压;

-

Force and sense lines

为了提升 PMU 驱动电压的精确度,常使用 4 条线路的结构:两条驱动线路传输电流,另两条感知线路监测我们感兴趣的点(通常是 DUT )的电压。这缘于欧姆定律 大家知道,任何线路都有电阻,当电流流经线路会在其两端产生压降,这样我们给到 DUT 端的电压往往小于我们在程序中设置的参数。设置两根独立的(不输送电流)感知线路去检测 DUT 端的电压,反馈给电压源,电压源再将其与理想值进行比较,并作相应的补偿和修正,以消除电流流经线路产生的偏差。驱动线路和感知线路的连接点被称作“开尔文连接点”。

-

量程设置

PMU 的驱动和测量范围在编程时必须被选定,合适的量程设定将保证测试结果的准确性。需要提醒的是, PMU 的驱动和测量本身就有就有范围的限制,驱动的范围取决于 PMU的最大驱动能力,如果程序中设定 PMU 输出 5V 的电压而 PMU 本 身设定为输出 4V 电压的话,最终只能输出 4V 的电压。同理,如果电流测量的量程被设定为 1mA ,则无论实际电路中电流多大,能测到的读数不会超过 1mA 。值得注意的是, PMU 上无论是驱动的范围还是测量的量程,在连接到 DUT 的时候都不应该再发生变化。这种范围或量程的变化会引起噪声脉冲(浪涌),是一种信号电压值短时间内的急剧变化产生的瞬间高压,类似于 ESD 的放电,会对 DUT 造成损害。

-

钳位设置

大多数 PMU 会被测试程序设置钳制电压和电流,钳制装置是在测试期间控制 PMU输出电压与电流的上限以保护测试操作人员、测试硬件及被测器件的电路。

-

limit卡控设置

PMU 有上限和下限这两个可编程的测量边界, 它们可以单独使用(如某个参数只需要小于或大于某个值)或者一起使用。实际测量值大于上限或小于下限的器件,均会被系统判为不良品。

-

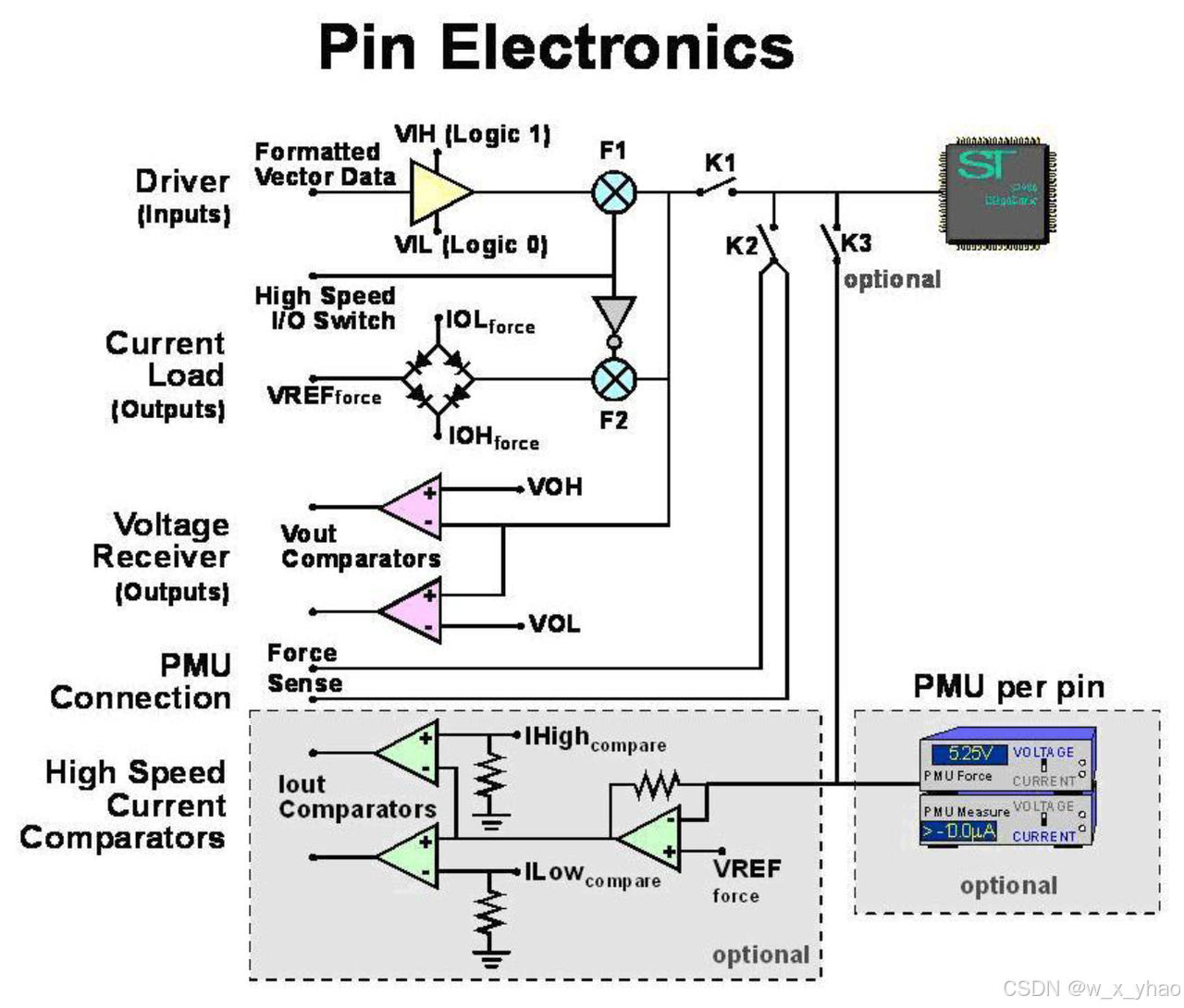

Pin Electronics

管脚电路( The Pin Electronics ,也叫 PinCard 、 PE 、 PEC 或 I/O Card )是测试系统资源部和待测器件之间的接口,它给待测器件提供输入信号并接收待测器件的输出信号。器件之间的接口,它给待测器件提供输入信号并接收待测器件的输出信号。

-

驱动单元(Driver)

驱动电路从测试系统的其他相应环节获取格式化的信号,称为FDATA,当FDATA通过驱动电路,从参考电压源(RVS)获取的VIL/VIH参考电平被施加到格式化的数据上。如果 FDATA命令驱动单元去驱动逻辑0,则驱动单元会驱动VIL参考电压; VIL Voltage In Low )指施加到 DUT的input 管脚仍能被DUT内部电路识别为逻辑0的最高保证电压。

如果FDATA命令驱动单元去驱动逻辑1,则驱动单元会驱动 VIH 参考电压;VIH(Voltage In High)指施加到DUT的input管脚仍能被 DUT 内部电路识别为逻辑 1 的最低保证电压。F1场效应管用于隔离驱动电路和待测器件,在进行输入 输出切换时充当快速开关角色。当测试通道被程序定义为输入(Input),场效应管F1导通,开关(通常是继电器)K1 闭合,使信号由驱动单元(Driver)输送至 DUT ;当测试通道被程序定义为输出 Output )或不关心状态 don’t care F1截止,K1断开,则驱动单元上的信号无法传送到DUT上。F1只可能处于其中的一种状态,这样就保证了驱动单元和待测器件同时向同一个测试通道送出电压信号的I/O冲突状态不会出现。

-

电流负载电源(Current Load)

电流负载(也叫动态负载)在功能测试时连接到待测器件的输出端充当负载的角色,由程序控制,提供从测试系统到待测器件的正向电流或从待测器件到测试系统的负向电流。电流负载提供 IOH(Current Output High )和 IOL Current Output Low )。IOH 指当待测器件输出逻辑 1 时其输出管脚必须提供的电流总和;IOL则相反,指当待测器件输出逻辑 0 时其输出管脚必须接纳的电流总和。当测试程序设定了IOH和IOL VREF电压就设置了它们的转换点。转换点决定了 IOH 起作用还是 IOL 起作用:当待测器件的输出电压高于转换点时,IOH提供电流;当待测器件的输出电压低于转换点时,IOL提供电流。F2和F1一样,也是一个场效应管,在输入输出切换时充当高速开关,并隔离电流负载电路和待测器件。当程序定义测试通道为输出,则 F2 导通,允许输出正向电流或抽取反向电流;当定义测试通道为输入,则F2截止,将负载电路和待测器件隔离。电流负载在三态测试和开短路测 试中也会用到。

-

电压比较单元( Voltage Receiver)

电压比较器用于功能测试时比较待测器件的输出电压和 RVS 提供的参考电压。 RVS 为有效的逻辑 1 VOH )和逻辑0 VOL)提供了参考:当器件的输出电压等于或小于VOL,则认为它是逻辑0;当器件的输出电压等于或大于 VOH ,则认为它是逻辑1;当它大于VOL而小于VOH,则认为它是三态电平或无效输出。

-

PMU连接点(PMU Connection)

当PMU连接到器件管脚,K1先断开,然后K2闭合,用于将PMU和Pin Electrics卡的I/O 电路隔离开来。

-

高速电流比较单元( High Speed Current Comparators)

相对于为每个测试通道配置 PMU ,部分测试系统提供了快速测量小电流的另一种方法,这就是可进行快速漏电流( Leakage )测试的电流比较器,开关 K3 控制它与待测器件的连接与否。如果测试系统本身就是 Per Pin PMU 结构的,那么这部分就不需要了。

-

PPPMU(Per Pin PMU)

一些系统提供 Per Pin PMU 的电路结构,以支持对 DUT 每个管脚同步地进行电压或电流测试。与 PMU 一样, PPPMU 可以驱动电流测量电压或者驱动电压测量电流,但是标准测试系统的PMU的其它功能 PPPMU 则可能不具备。

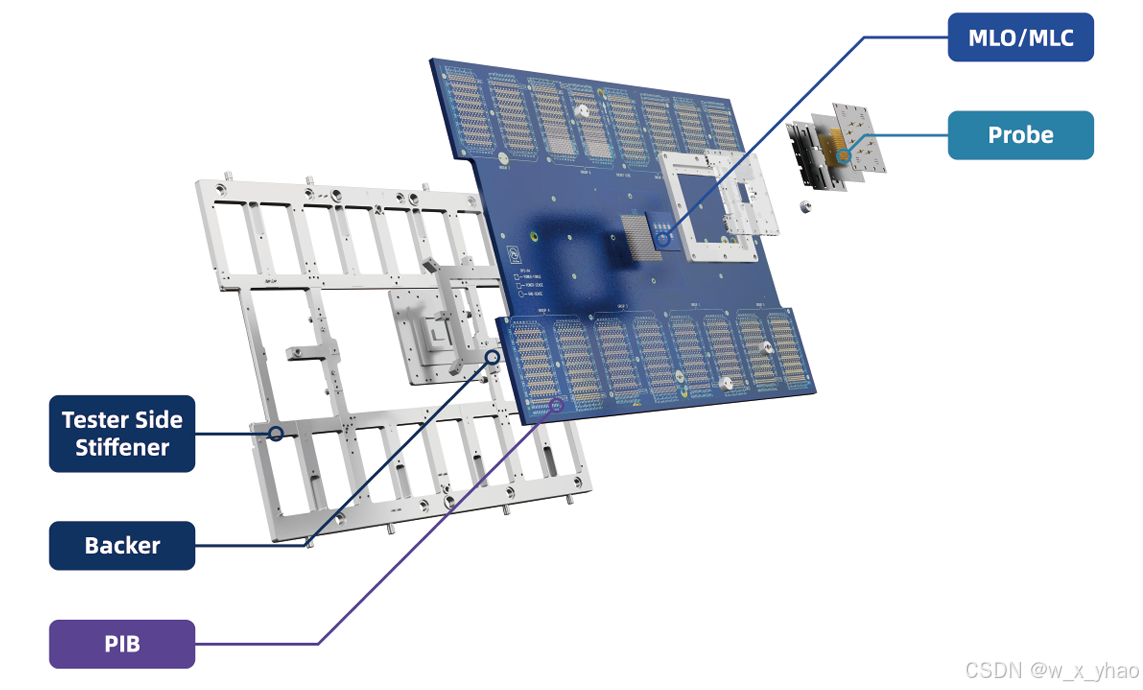

LB/PC

-

如下图,LB/PC是一种高性能的多层电路板,用于在生产过程中测试半导体器件。它被设计成与半导体器件和测试设备接口,对器件进行电气测试,并验证其功能、性能和可靠性。

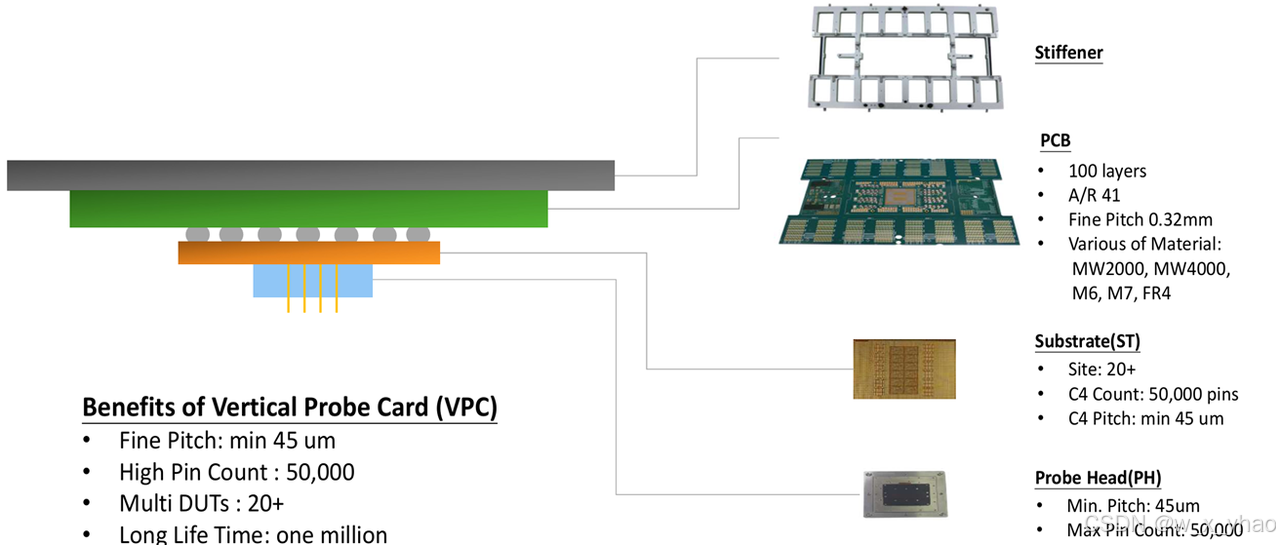

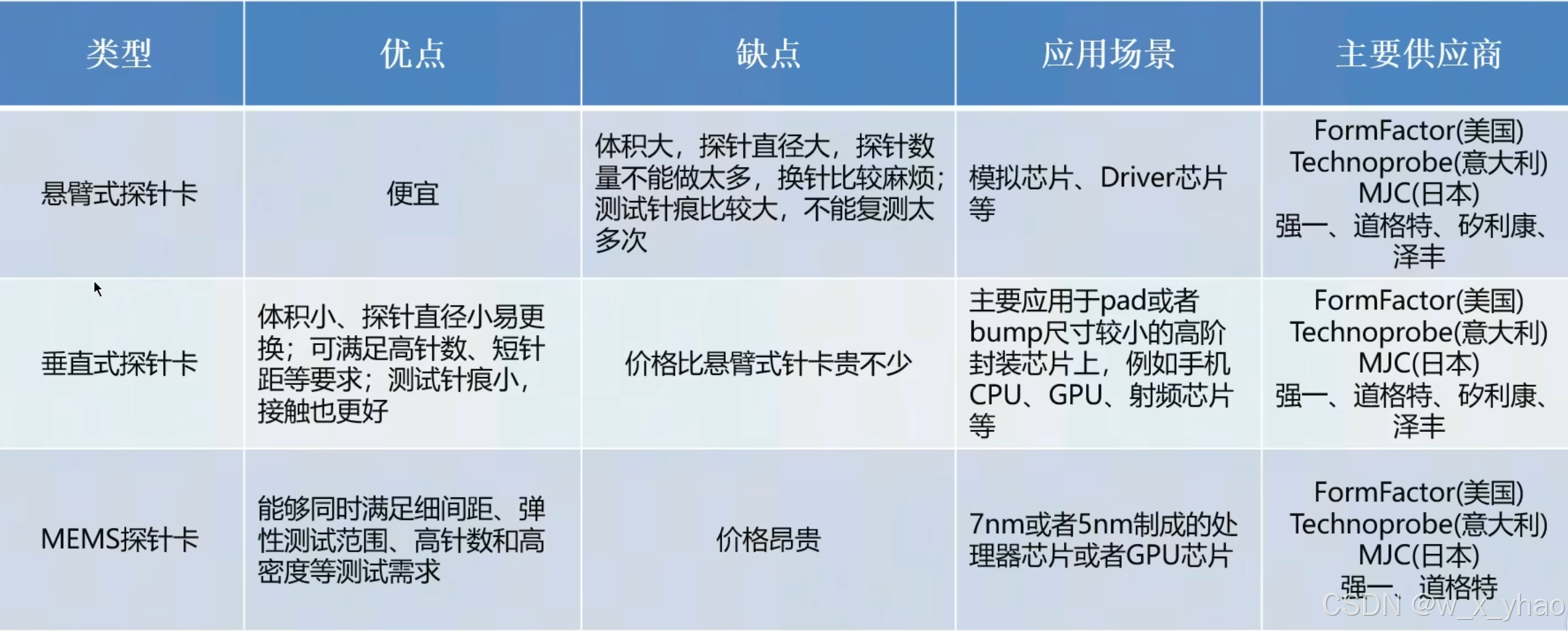

ProbeCard

-

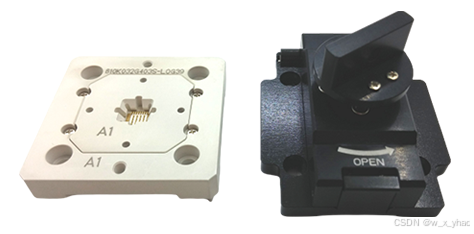

Socket

Socket,用于FT、SLT、EVB等测试,是连接被测器件(DUT)和测试设备的关键接口装置;

-

ChangeKit

ChangeKit作为Handler的配套治具,装于Handler上,用于将待测芯片以队列形式进出ATE机台;如下图,KIT箱中包含以下器具:Socket(左下)、shuttle(梭子)(右下)、Hot plate(预热盘)(上)、Clamp(压头)(中);

Shuttle(梭子):将未测试残片由Tray 或 Sock Buffer(Hot Plate)传送到测试区(Test Site)。或将已测产品送至Output Tray。部分的测试机台在I/O Shuttle有加热功能,以保持测试品的温度。

Hot plate(预热盘):预热DUT,以便达到客户要求的测试温度;

Clamp(Contactor set,压头):安装于测试头(Test Arm)上,自Shuttle取货并送至测试座(Socket)中。在测货过程中,提供稳定的压力,以达到产品与Socket紧密接触的目的。

-

Hander

Handler,用于FT、SLT量产测试,主要作用是与ATE机台协同工作,通过机械臂和气嘴对芯片进行预热、移送,并为芯片提供下压力,使芯片的ball与LB上的探针紧密连接。

Handler运作视频:https://www.bilibili.com/video/BV1gz4y1D7BN/?spm_id_from=333.337.search-card.all.click

-

Prober

探针台,用于CP测试,主要作用是承载晶圆,并不断移送DUT,使得探针卡上的探针可以和芯片管脚连接。

探针台运作视频:https://www.bilibili.com/video/BV1fu4m1N7xk/?spm_id_from=333.337.search-card.all.click

https://download.csdn.net/blog/column/12249191/134226743

https://mp.weixin.qq.com/s?__biz=MzUyOTY5NzkwNg==&mid=2247486943&idx=1&sn=3ff710a9799ce76324d10005f06974ef&chksm=fa5c50c2cd2bd9d482de0aa0a25558e6281970d58e96769ccc416f1b71b85acb0185a4446b38&token=1427783553&lang=zh_CN#rd

https://mp.weixin.qq.com/s?__biz=MzUyOTY5NzkwNg==&mid=2247487174&idx=1&sn=229d81fe1c8c7b4045afceb630bea6b8&chksm=fa5c53dbcd2bdacd8a53b2d5c0091ddff0d1a758977fd01806c6dc7fbf47a5c84ff628b594a3&token=1427783553&lang=zh_CN#rd

https://mp.weixin.qq.com/s?__biz=MzUyOTY5NzkwNg==&mid=2247486818&idx=1&sn=421077dcfcb245a8ac37c0840f1ee0ac&chksm=fa5c507fcd2bd96930e1b21a84a221abaef1d25f0cfdfe4ab29684c160d4df37a416564da37a&token=1427783553&lang=zh_CN#rd

https://blog.csdn.net/smartvxworks/article/details/132490951?ops_request_misc=%257B%2522request%255Fid%2522%253A%252286f21a53a3743dcd5d61f49c23c392dc%2522%252C%2522scm%2522%253A%252220140713.130102334..%2522%257D&request_id=86f21a53a3743dcd5d61f49c23c392dc&biz_id=0&utm_medium=distribute.pc_search_result.none-task-blog-2~all~top_click~default-4-132490951-null-null.142^v100^pc_search_result_base7&utm_term=%E8%8A%AF%E7%89%87%E6%B5%8B%E8%AF%95&spm=1018.2226.3001.4187

https://blog.csdn.net/qq_50998481/article/details/138485917?ops_request_misc=%257B%2522request%255Fid%2522%253A%2522eedae61054ae4fc191f7d600ca61072b%2522%252C%2522scm%2522%253A%252220140713.130102334.pc%255Fblog.%2522%257D&request_id=eedae61054ae4fc191f7d600ca61072b&biz_id=0&utm_medium=distribute.pc_search_result.none-task-blog-2~blog~first_rank_ecpm_v1~rank_v31_ecpm-1-138485917-null-null.nonecase&utm_term=ate&spm=1018.2226.3001.4450

https://www.cti-cert.com/new/25196.html

https://blog.csdn.net/qq_36033382/article/details/125451961