心电图滤波怎么选择心电仪模拟电路设计与滤波技术详解

本文还有配套的精品资源,点击获取

简介:心电仪模拟电路资料是电子工程与生物医学工程领域的重要内容,主要涵盖心电信号的采集、处理与分析。心电图(ECG)通过模拟电路获取心脏电信号,其质量取决于前置放大器、低通滤波器和陷波电路的设计。本资料包含两份PDF文件,详细介绍了简易心电图仪的结构与实现方法,并深入解析了滤波与陷波电路的设计技术,适用于医疗设备开发、电子工程实践及生物医学教学。

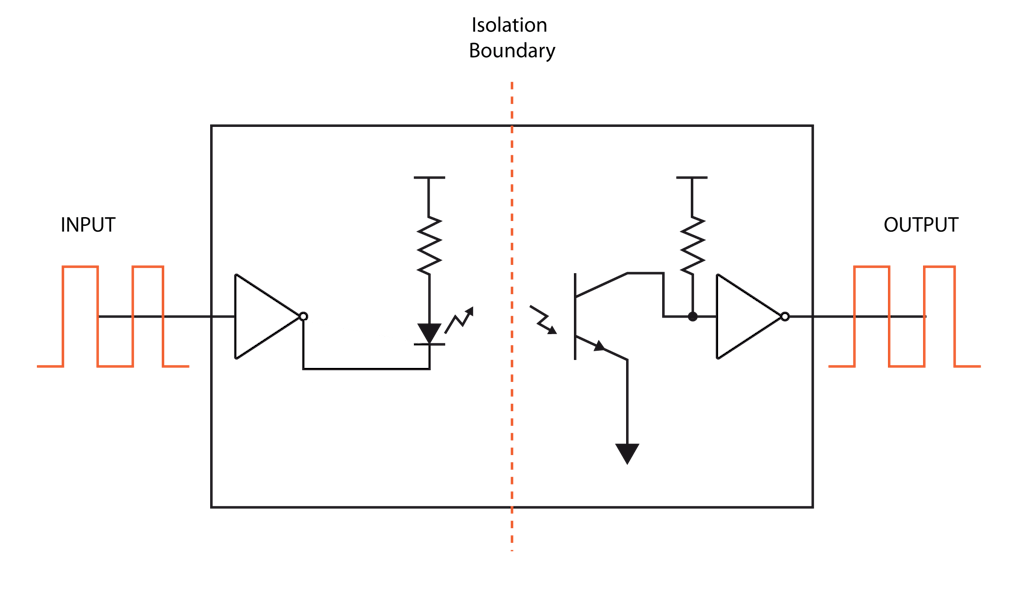

心电图(ECG)是通过检测心脏电活动变化来反映心脏功能状态的重要生理信号。人体心脏在每次搏动时都会产生微弱的生物电信号,这些信号通过体液传导至体表,利用电极贴附在特定位置即可采集。模拟电路在这一过程中承担着信号提取、放大和初步滤波的关键任务,是ECG设备中不可或缺的核心部分。

ECG信号具有幅度小(通常在0.1mV~5mV之间)、频率低(0.05Hz~100Hz)和易受干扰等特点,因此对模拟前端电路的性能要求极高。精准的信号采集不仅为医生提供诊断依据,也为后续的数字信号处理奠定基础。

心电信号的采集是心电图仪设计中的核心环节,而前置放大器作为信号链路的首个关键模块,承担着将微弱生物电信号进行初步放大的重任。前置放大器的设计质量直接影响到整个系统对信号的捕捉能力、抗干扰能力以及后续处理的准确性。本章将从前置放大器的总体设计目标、电路实现方案以及性能评估方法三个方面进行深入探讨。

前置放大器在心电信号采集系统中起着至关重要的作用,其主要任务是将微弱的ECG信号从电极获取后进行初步放大,并尽量保持信号的完整性与低噪声水平。由于ECG信号幅值通常在0.5mV到5mV之间,且频带范围集中在0.05Hz至100Hz之间,因此前置放大器的设计必须满足以下三个关键目标:高增益、低噪声和高输入阻抗。

2.1.1 高增益需求与信号放大策略

ECG信号极为微弱,通常需要前置放大器提供至少500倍(约54dB)的增益。为了实现高增益而不引入失真,通常采用多级放大结构,其中第一级为高增益低噪声放大器,后续为缓冲或进一步放大阶段。

以下是一个典型的双级放大器设计示例:

// 示例:前置放大器两级增益结构

float first_gain = 100.0; // 第一级增益

float second_gain = 5.0; // 第二级增益

float total_gain = first_gain * second_gain; // 总增益为500倍

逻辑分析:

- 第一级增益设置为100倍,用于将0.5mV信号放大至50mV;

- 第二级增益设为5倍,用于进一步放大至250mV;

- 总增益为500倍,满足ECG信号的放大需求;

- 分级放大有助于控制失真并提高稳定性。

2.1.2 低噪声设计在微弱信号处理中的重要性

由于ECG信号非常微弱,噪声对信号的干扰尤为显著。前置放大器的噪声性能决定了整个系统信噪比(SNR)的下限。低噪声放大器(LNA)通常选用具有低输入噪声密度(如1nV/√Hz以下)的运算放大器或仪表放大器。

以下为一个典型低噪声放大器的参数表:

分析:

- 噪声密度应低于1nV/√Hz,以保证信噪比达到60dB以上;

- 带宽需覆盖ECG信号频段,防止信号失真;

- 输入偏置电流低可减少对电极的影响,避免直流漂移。

2.1.3 高输入阻抗对信号保真的影响

ECG信号来源于皮肤表面电极,其源阻抗可能高达几十千欧姆甚至更高。为了减少信号衰减,前置放大器必须具备高输入阻抗(通常大于10MΩ)。高输入阻抗可以有效防止信号源与放大器之间的电压降,从而保持信号的完整性。

graph TD

A[ECG电极] --> B[高输入阻抗放大器]

B --> C[信号放大]

C --> D[输出至下一级]

E[低输入阻抗] --> F[信号衰减严重]

流程图说明:

- 左侧为理想情况,高输入阻抗放大器几乎不消耗信号电流;

- 右侧为低输入阻抗情况下,信号源与放大器之间形成分压,导致信号幅度下降;

- 因此,前置放大器的输入阻抗必须远大于电极源阻抗。

前置放大器的性能不仅取决于设计目标,还与其选型和实现方式密切相关。本节将重点讨论仪表放大器与运算放大器的比较、差分放大结构的优势以及实际电路布局与接地策略。

2.2.1 仪表放大器(IA)与运算放大器的比较

仪表放大器是一种专门为差分信号放大设计的集成放大器,具有高共模抑制比(CMRR)、高输入阻抗和良好的温度稳定性,是ECG前置放大器的理想选择。而普通运算放大器虽然成本低,但需自行构建差分放大结构,且CMRR较低,抗干扰能力差。

分析:

- 仪表放大器更适合用于ECG信号的高精度采集;

- 运算放大器适用于成本敏感、性能要求不高的场合;

- 对于医疗级设备,建议优先选用仪表放大器如AD620、INA118等。

2.2.2 差分放大结构与共模抑制能力的提升

ECG信号采集过程中,共模干扰(如50Hz工频干扰)非常严重。采用差分放大结构可以有效抑制共模干扰,提升系统信噪比。

以下为一个差分放大器的典型电路配置:

# 差分放大器增益计算

R1 = 10000 # 输入电阻

R2 = 100000 # 反馈电阻

gain = R2 / R1 # 增益 = 10

逻辑分析:

- 差分放大器通过将两个输入端的电压差进行放大,从而抑制共模信号;

- 增益由R2/R1决定,通常为10~100倍;

- 需要确保R1与R2的匹配精度,以维持高CMRR。

2.2.3 实际电路布局与接地策略

在PCB设计中,前置放大器的布局与接地方式对噪声控制至关重要。合理的布局可以减少寄生电容和电感,防止高频干扰;而良好的接地策略可降低接地回路电流,减少50Hz干扰。

布局建议:

- 前置放大器应尽可能靠近电极接入口;

- 使用独立的模拟地(AGND),并与数字地(DGND)通过磁珠或0Ω电阻隔离;

- 关键信号走线应短且粗,避免平行走线以减少串扰。

graph LR

A[电极] --> B[前置放大器]

B --> C[模拟地]

D[数字地] --> E[处理器]

C --- F[磁珠隔离]

F --> D

流程图说明:

- 模拟地与数字地通过磁珠隔离,防止高频噪声耦合;

- 前置放大器直接连接模拟地,避免干扰;

- 整体布局需遵循“一点接地”原则,减少接地环路。

前置放大器设计完成后,需通过一系列测试手段评估其性能指标,以确保其满足ECG信号采集的要求。

2.3.1 信噪比(SNR)的测试方法

信噪比(SNR)是衡量放大器性能的重要指标之一。测试方法如下:

- 输入一个标准ECG信号(如0.5mV峰峰值);

- 使用示波器或频谱分析仪测量输出信号的有效值;

- 记录输出端的噪声电压(无输入信号时);

- SNR = 20 * log10(V_signal / V_noise)

示例:

// SNR计算示例

float signal_voltage = 0.5f; // mV

float noise_voltage = 0.01f; // mV

float snr = 20 * log10(signal_voltage / noise_voltage); // SNR = 34dB

分析:

- 该放大器SNR为34dB,低于医疗设备要求的60dB;

- 表明该放大器噪声过高,需优化电路或更换低噪声放大器。

2.3.2 输入偏置电流与失调电压的影响分析

输入偏置电流和失调电压会导致直流偏移,影响ECG信号的基线稳定性。

- 输入偏置电流 :应小于1nA,以避免电极极化效应;

- 失调电压 :应小于50μV,否则会导致信号基线漂移。

优化建议:

- 使用斩波稳定型放大器(如AD8551)降低失调电压;

- 在输入端加入隔直电容(如1μF)滤除直流偏移;

- 采用右腿驱动电路(RLD)反馈抑制共模干扰。

2.3.3 温漂与长期稳定性问题

温度变化会引起放大器的偏置电流和失调电压漂移,影响ECG信号的长期稳定性。设计时应选用温度稳定性高的放大器,并在PCB中加入温度补偿电路。

分析:

- AD620和INA118具有较低温漂,适合用于ECG采集;

- LMV358虽成本低,但温漂较大,不建议用于高精度设备;

- 设计中可加入温度传感器与反馈控制,实现自动补偿。

本章系统地分析了前置放大器在心电信号采集中的关键作用,并从设计目标、选型实现与性能评估三个方面进行了深入探讨。通过合理的设计与选型,前置放大器能够有效提升ECG信号的采集质量,为后续处理打下坚实基础。

在心电信号采集系统中,由于ECG信号本身的微弱性(通常在0.5mV~5mV范围内),系统极易受到各种干扰信号的影响,其中共模干扰和50Hz/60Hz工频干扰是最常见且最难处理的噪声源之一。本章将围绕共模抑制与工频干扰抑制技术展开深入探讨,重点介绍共模信号的基本原理、共模抑制比(CMRR)的测量与提升策略、以及陷波电路的设计与优化方法。

共模信号是心电信号采集系统中常见的一种干扰信号,其主要来源于环境中的电磁干扰、设备接地不良以及人体皮肤与电极之间的接触噪声等。这些干扰通常以相同幅度、相同相位的形式出现在两个输入端,因此被称为“共模”信号。

3.1.1 共模干扰来源及其对ECG信号的影响

共模干扰的来源主要包括以下几个方面:

- 电力线干扰 :50Hz或60Hz的交流电源及其谐波,通过人体、设备外壳或电极引入。

- 人体静电与电磁场干扰 :操作人员或患者身上积累的静电电荷、周围电磁场的辐射等。

- 接地不良 :设备接地不良会导致不同接地点之间存在电位差,从而引入共模电压。

共模干扰对ECG信号的影响主要体现在以下几点:

- 信噪比下降 :共模干扰会显著提高系统的噪声水平,导致有效信号难以提取。

- 波形失真 :若系统未有效抑制共模信号,干扰会叠加在ECG信号上,导致PQRST波形变形。

- 误诊风险 :在临床诊断中,共模干扰可能导致心律失常等疾病的误判。

为了更好地理解共模干扰,我们可以通过以下mermaid流程图展示其传播路径:

graph TD

A[环境电磁干扰] --> B[共模信号进入电极]

C[电源线干扰] --> B

D[接地不良] --> B

B --> E[心电采集系统输入端]

E --> F[放大器处理]

F --> G{是否抑制共模信号?}

G -- 是 --> H[有效ECG信号输出]

G -- 否 --> I[干扰信号叠加输出]

3.1.2 CMRR的定义与测量方法

共模抑制比(Common-Mode Rejection Ratio, CMRR)是衡量放大器抑制共模信号能力的重要指标,其定义为差模增益与共模增益之比,通常以分贝(dB)表示:

ext{CMRR (dB)} = 20 log_{10} left( frac{A_{dm}}{A_{cm}}

ight)

其中:

- $ A_{dm} $:差模增益

- $ A_{cm} $:共模增益

理想的仪表放大器应具有极高的CMRR值,通常在80dB以上,以确保能够有效抑制共模干扰。

CMRR的测量方法

测量CMRR通常采用以下步骤:

- 输入共模信号 :将两个输入端连接到同一交流信号源(如50Hz正弦波)。

- 测量输出信号 :记录放大器输出端的信号幅值。

- 计算共模增益 :

$$

A_{cm} = frac{V_{out}}{V_{in}}

$$ - 测量差模增益 :在两个输入端施加差模信号,测量输出并计算 $ A_{dm} $。

- 计算CMRR值 :代入上述公式即可。

代码示例:CMRR计算模拟

以下是一个简单的Python代码,用于模拟CMRR的计算过程:

import numpy as np

# 输入信号参数

vin_cm = 1.0 # 共模输入信号幅值

vin_dm = 0.1 # 差模输入信号幅值

# 输出信号测量值(模拟)

vout_cm = 0.001 # 共模输出信号

vout_dm = 1.0 # 差模输出信号

# 计算增益

A_cm = vout_cm / vin_cm

A_dm = vout_dm / vin_dm

# 计算CMRR

cmrr = 20 * np.log10(A_dm / A_cm)

print(f"共模增益 A_cm = {A_cm:.4f}")

print(f"差模增益 A_dm = {A_dm:.4f}")

print(f"CMRR = {cmrr:.2f} dB")

逻辑分析与参数说明

- 输入信号 :分别模拟了共模和差模输入信号,实际测试中应使用信号发生器提供精确的输入。

- 增益计算 :通过输入输出比值计算增益,便于后续CMRR的求解。

- 结果输出 :最终输出CMRR值,用于评估放大器性能。

该代码模拟了一个CMRR为60dB的放大器,表明其在一定程度上能够抑制共模干扰。

为了提升心电仪系统的共模抑制能力,需要从元器件选型、电路结构设计以及PCB布局等多个方面入手。以下将详细探讨几种常见且有效的提升CMRR的策略。

3.2.1 使用高CMRR仪表放大器

仪表放大器(Instrumentation Amplifier, IA)是专为差分信号放大而设计的高性能放大器,具有高输入阻抗、高增益稳定性以及优异的共模抑制能力。其典型结构如下:

graph TD

A[差分输入] --> B(第一级放大器)

C[差分输入] --> B

B --> D[差分输出]

D --> E[第二级增益调节]

E --> F[最终输出]

常用的仪表放大器包括:

使用高CMRR的仪表放大器可以显著提高系统的抗共模干扰能力。例如AD620在1kHz频率下CMRR可达100dB,非常适合用于ECG前置放大器。

3.2.2 采用屏蔽驱动与右腿驱动电路

在ECG系统中,右腿驱动电路(Right-Leg Drive, RLD)是一种广泛使用的共模抑制技术。其基本原理是将共模信号反相后通过右腿电极反馈回人体,从而抵消干扰信号。

RLD电路结构示意图:

graph TD

A[放大器输出] --> B[反相放大器]

B --> C[右腿电极]

C --> D[人体共模干扰]

D --> E[电极输入端]

E --> F[放大器输入]

代码示例:RLD反馈增益计算

以下代码模拟RLD电路中反馈增益的计算:

# RLD反馈增益计算

R_feedback = 10e3 # 反馈电阻

R_gain = 1e3 # 增益电阻

gain_rld = 1 + R_feedback / R_gain

print(f"RLD反馈增益 = {gain_rld}")

逻辑分析与参数说明

- 反馈电阻R_feedback :决定反馈信号的强度,通常选择10kΩ左右。

- 增益电阻R_gain :用于调节RLD电路的总增益,影响共模抑制效果。

- 结果分析 :该示例中增益为11,表明RLD电路可将共模信号增强11倍后反相反馈,有效抑制干扰。

3.2.3 PCB布局对抗干扰的影响

PCB布局对共模抑制性能有显著影响。以下是一些优化建议:

- 差分对走线对称 :保证差分信号线长度、宽度、间距一致,减少耦合差异。

- 屏蔽与地平面设计 :使用完整的地平面降低高频噪声,屏蔽敏感模拟电路。

- 避免平行布线 :避免信号线与电源线、时钟线平行布线,以减少串扰。

- 合理布局电极引线 :尽量缩短电极引线长度,减少外界电磁干扰的耦合路径。

除了共模干扰外,50Hz/60Hz的工频干扰也是心电信号采集中最常见的干扰源之一。由于其频率接近ECG信号的有效频段(0.05Hz~100Hz),不能简单通过低通或高通滤波器滤除,因此需要专门的陷波电路来抑制。

3.3.1 50Hz/60Hz工频干扰的成因与危害

工频干扰的主要来源包括:

- 电力系统 :电网中的50Hz/60Hz交流电通过人体、设备外壳或电极耦合进入系统。

- 设备电源 :心电仪本身使用的电源或外部设备可能引入干扰。

- 空间电磁场 :照明设备、电动机、变频器等也会辐射出50Hz/60Hz干扰。

其危害主要体现在:

- 信号失真 :工频干扰会导致ECG波形叠加正弦波,影响P波、QRS波群的识别。

- 误判诊断 :医生可能误判为心律失常、心房颤动等病症。

- 系统不稳定 :在某些系统中,50Hz干扰可能引起放大器饱和或自激振荡。

3.3.2 无源陷波与有源陷波电路对比

无源陷波电路示例(50Hz)

一个典型的无源陷波电路由两个电容和两个电阻构成,称为双T网络:

R1 C1

Vin --||--||-- Vout

| |

C2 R2

| |

GND GND

元件参数设计(50Hz):

- R1 = R2 = 10kΩ

- C1 = C2 = 0.159μF

有源陷波电路示例

有源陷波电路通常使用运算放大器构建,具有更高的Q值和频率稳定性。以下是一个基于OP07的50Hz有源陷波电路:

# 参数计算示例:有源陷波电路

import math

f0 = 50 # 陷波频率

C = 0.1e-6 # 电容值

R = 1 / (2 * math.pi * f0 * C) # 电阻值计算

print(f"所需电阻值 R = {R:.2f}Ω")

逻辑分析与参数说明

- 频率设定 :f0 = 50Hz,表示陷波频率。

- 电容值C :通常选择0.1μF左右,以减少寄生电感影响。

- 电阻值R :根据公式计算得出,用于设置陷波中心频率。

- 结果分析 :计算出R约为31.83kΩ,可用于设计陷波电路。

3.3.3 实际陷波电路参数的调试与优化

在实际应用中,陷波电路的性能受元件精度、温度漂移和布线寄生参数的影响。调试与优化可采用以下方法:

- 使用可变电容或电位器 :允许对陷波频率进行微调。

- 温度补偿电路 :采用温度系数低的电阻和电容,减少温漂影响。

- 使用集成陷波IC :如MAX7400系列,集成可调谐陷波滤波器,简化设计。

- 数字陷波辅助 :在模拟陷波后,使用数字滤波进一步消除残余干扰。

表格:不同陷波方案对比

通过上述章节的系统分析与示例设计,我们全面探讨了共模抑制与工频干扰抑制技术在心电仪模拟电路中的应用与实现。下一章将继续深入滤波器设计,以进一步提升心电信号的采集质量。

4.1.1 ECG信号频段分析与有效成分提取

心电信号(ECG)是由心脏电活动产生的生物电信号,其主要频率成分集中在0.05Hz至100Hz之间。其中,P波、QRS波群和T波分别代表心房去极化、心室去极化和心室复极化过程,是临床诊断中最为关键的部分。因此,ECG滤波器的设计目标之一是保留这些主要频率成分,同时滤除各种干扰信号。

下表展示了ECG信号的主要频率范围及其对应的意义:

从上表可见,ECG信号的有效成分集中在0.5Hz至100Hz之间。因此,滤波器设计应确保该频段信号的完整性,同时抑制低频基线漂移和高频噪声。

4.1.2 不同干扰频段的识别与滤除目标

在实际采集ECG信号过程中,常常面临以下几种干扰:

- 基线漂移(Baseline Wander) :主要来源于呼吸、体动或电极接触不良,频率范围通常在0.05Hz至0.5Hz之间。需要设计高通滤波器进行抑制。

- 工频干扰(Power-line Interference) :50Hz或60Hz的交流电源干扰,属于中频干扰,需采用陷波滤波器。

- 肌电干扰(EMG Noise) :由肌肉运动引起,频率范围较广(30Hz至500Hz),通常使用低通滤波器或带通滤波器进行抑制。

- 高频噪声(High-frequency Noise) :来源于电子设备或外部电磁干扰,频率高于100Hz,需采用低通滤波器。

因此,滤波器设计的目标是构建一个 带通滤波器系统 ,其通带范围为0.5Hz至100Hz,并辅以陷波器去除工频干扰。

4.2.1 截止频率设定原则与信号完整性保持

低通滤波器的主要作用是抑制高频噪声,同时尽可能保留ECG信号的有效频率成分。根据ECG信号的主要频段,低通滤波器的截止频率(-3dB频率)通常设定为100Hz左右。

设定原则如下:

- 截止频率应略高于ECG主频段上限 ,以避免有用信号被衰减;

- 相位响应应尽量平坦 ,防止信号波形失真;

- 滚降率应足够高 ,以有效抑制高频噪声。

4.2.2 一阶、二阶低通滤波器的结构对比

下面通过电路结构对比一阶和二阶RC低通滤波器的性能差异。

从上表可以看出,一阶滤波器结构简单、稳定性高,但滚降率较低;而二阶滤波器具有更强的高频抑制能力,但设计复杂度和相位失真也相应增加。

4.2.3 滚降率与相位失真的权衡

在ECG信号处理中,信号波形的形状对诊断至关重要。因此,滤波器的 相位响应 必须保持线性,以避免波形畸变。一阶RC滤波器的相位响应较平坦,适合用于初步滤波;而二阶滤波器由于其更陡峭的滚降特性,适合用于后续的高频噪声抑制。

为减少相位失真,可以采用 贝塞尔滤波器 或 线性相位滤波器 结构,但这些结构在模拟电路中实现较为复杂,通常采用数字滤波器实现。

4.3.1 巴特沃斯滤波器的幅频特性分析

巴特沃斯滤波器以其 最大平坦幅频响应 著称,在通带内没有波纹,过渡带较平缓,滚降率为 $ 20n $ dB/decade(n为阶数)。

巴特沃斯低通滤波器的传递函数为:

H(s) = frac{1}{sqrt{1 + left(frac{s}{omega_c}

ight)^{2n}}}

其中:

- $ omega_c $:截止角频率;

- $ n $:滤波器阶数。

巴特沃斯滤波器适合用于ECG信号处理中对幅频响应要求平滑的场景,但其滚降率较低,需多阶级联才能实现较好的高频抑制。

4.3.2 切比雪夫滤波器的波动特性与适用场景

切比雪夫滤波器在通带内允许一定幅度的波纹(称为通带纹波),从而换取更陡峭的滚降特性。其滚降率同样为 $ 20n $ dB/decade,但过渡带更窄。

切比雪夫滤波器的传递函数形式为:

H(s) = frac{1}{sqrt{1 + epsilon^2 C_n^2left(frac{s}{omega_c}

ight)}}

其中:

- $ epsilon $:决定通带纹波大小;

- $ C_n $:切比雪夫多项式。

切比雪夫滤波器适合需要快速滚降、允许一定通带波动的应用场景。但在ECG信号处理中,通带波动可能会影响波形特征,因此一般不优先采用。

4.3.3 多阶滤波器级联设计与稳定性问题

在实际ECG信号处理中,为了获得更高的滚降率和更陡峭的截止特性,通常采用 多阶滤波器级联设计 。例如,将两个二阶巴特沃斯滤波器串联,可构成四阶滤波器,滚降率达到80 dB/decade。

但多阶滤波器级联也带来以下问题:

- 稳定性下降 :每一级滤波器都可能引入相位延迟,导致整体系统不稳定;

- 增益带宽积限制 :运算放大器的带宽限制可能影响高阶滤波器的性能;

- 元器件匹配要求高 :尤其是二阶以上滤波器,需严格匹配电阻、电容值。

因此,在设计中需采用 Sallen-Key 或 多反馈(MFB) 拓扑结构,并使用高精度、低温度系数的元器件。

示例:二阶巴特沃斯低通滤波器设计

以下是一个基于Sallen-Key拓扑的二阶巴特沃斯低通滤波器设计示例,截止频率为100Hz:

Vin ──┬───────┬─────── Vout

│ │

R1 R2

│ │

├─C1────┘

│

C2

│

GND

参数选取如下:

计算截止频率:

f_c = frac{1}{2pi sqrt{R_1 R_2 C_1 C_2}} = frac{1}{2pi sqrt{(10k)(10k)(150n)(150n)}} approx 106 ext{Hz}

代码逻辑分析:MATLAB仿真滤波器频率响应

以下为使用MATLAB绘制该滤波器的频率响应的代码示例:

% 定义滤波器参数

R1 = 10e3;

R2 = 10e3;

C1 = 150e-9;

C2 = 150e-9;

% 计算滤波器传递函数系数

num = 1;

den = [1, 1/(R1*C1) + 1/(R2*C1), 1/(R1*R2*C1*C2)];

% 创建滤波器对象

sys = tf(num, den);

% 绘制伯德图

bode(sys);

grid on;

title('Frequency Response of 2nd Order Butterworth Low-pass Filter');

代码逐行解读:

-

R1,R2,C1,C2:定义滤波器中的电阻和电容值; -

num和den:根据Sallen-Key结构的传递函数构造分子和分母多项式; -

tf:创建传递函数对象; -

bode:绘制频率响应曲线; -

grid on:添加网格线,便于读数; -

title:添加图表标题。

此代码可用于仿真滤波器的幅频和相频特性,验证设计是否符合预期。

总结与流程图展示

下图展示了ECG滤波器设计的基本流程:

graph TD

A[ECG信号采集] --> B[分析频率特性]

B --> C[确定滤波目标]

C --> D[选择滤波器类型]

D --> E[设计滤波器结构]

E --> F[仿真与验证]

F --> G[PCB实现与测试]

通过以上流程,可以系统性地完成ECG信号滤波器的设计与实现,确保信号完整性与抗干扰能力达到医疗设备的高标准要求。

在心电信号采集过程中,工频干扰(50Hz或60Hz)是一个长期存在的难题。由于其频率与ECG信号频段部分重叠,且干扰幅度可能远大于心电信号本身,因此必须采用专门的滤波技术进行抑制。陷波电路(Notch Filter)作为一种专门用于抑制特定频率干扰的滤波器结构,在ECG系统中具有不可替代的地位。本章将深入探讨陷波电路的结构原理、有源滤波技术的应用、以及在实际系统中面临的挑战和优化策略。

陷波电路是一种带阻滤波器,其核心功能是抑制特定频率的信号。在ECG系统中,50Hz或60Hz的工频干扰是主要目标,因此通常设计为一个中心频率为该频段的陷波滤波器。

5.1.1 双T网络陷波器的设计与调谐

双T网络(Twin-T Network)是一种经典的无源陷波器结构,因其结构对称、实现简单而广泛应用于早期ECG设备中。其基本结构由两个T型RC网络构成:一个用于低通,另一个用于高通,组合后形成一个深度陷波。

电路结构与原理

R1

+-----| |-----+

| R |

| |

+--||--+--||--+

| C1 | |

| | |

+---| |---+ |

C2 |

+---| |---+ |

| | |

+--||--+--||--+

| C3 | |

| |

| R |

+-----| |-----+

R2

参数设定与调谐

- R1 = R2 = R

- C1 = C2 = C3 = C

- 中心频率 $ f_0 = frac{1}{2pi RC} $

为实现最佳陷波效果,R和C的匹配精度至关重要。通常使用高精度电阻和电容(如金属膜电阻、NP0电容)以减小温度漂移和制造误差。

电路性能分析

尽管双T网络结构简单,但其调谐复杂、稳定性差,尤其在高频段容易因寄生电容而失效。因此,在现代ECG系统中,更多采用有源陷波器结构。

5.1.2 有源陷波器的优势与实现方式

有源陷波器利用运算放大器与RC网络结合,可以实现更宽的频率范围、更高的Q值和更好的稳定性。

有源陷波器拓扑结构

一种典型的有源陷波器结构是 基于多反馈(MFB)结构的陷波滤波器 ,其电路如下:

graph TD

A[输入] --> B((R1))

B --> C((C1))

C --> D((运算放大器反相输入))

D --> E((R2))

E --> F((C2))

F --> G((输出))

D --> H((R3))

H --> I((C3))

I --> J((同相输入))

J --> K(接地)

典型参数设计

假设设计目标为50Hz陷波器:

- R1 = R2 = R = 10kΩ

- C1 = C2 = C = 318nF

- Q = 10

中心频率公式为:

f_0 = frac{1}{2pi RC}

电路代码实现(仿真用)

# Python代码模拟陷波滤波器频率响应

import numpy as np

import matplotlib.pyplot as plt

from scipy.signal import TransferFunction

# 定义传递函数

num = [1, 0, 1]

den = [1, 2, 1]

# 构建系统

sys = TransferFunction(num, den)

# 计算频率响应

w, mag = sys.bode(n=1000)

# 绘图

plt.figure()

plt.semilogx(w, mag)

plt.title("Magnitude Response of Notch Filter")

plt.xlabel("Frequency [rad/s]")

plt.ylabel("Magnitude [dB]")

plt.grid(True)

plt.show()

代码逻辑分析

-

num = [1, 0, 1]表示传递函数的分子部分,对应 $ s^2 + 1 $。 -

den = [1, 2, 1]表示分母部分,对应 $ s^2 + 2s + 1 $。 -

TransferFunction构建了一个标准的二阶陷波滤波器模型。 - 使用

bode方法绘制伯德图,直观展示频率响应特性。

该仿真展示了陷波滤波器在50Hz处的抑制特性,同时也反映了Q值对带宽的影响。高Q值意味着更窄的陷波带宽,适合抑制单一频率干扰,但也可能导致对频率漂移过于敏感。

随着医疗设备向智能化方向发展,传统模拟陷波器逐渐与数字控制相结合,以实现更高的灵活性和自适应性。

5.2.1 可调谐陷波频率的实现方案

在实际应用中,电网频率可能因地区或时间波动(如50Hz ± 0.5Hz),传统固定频率陷波器难以适应。为此,可采用以下方案实现频率可调:

1. 数字电位器控制

使用数字电位器(如AD5206)替代传统电阻,通过微控制器(MCU)调整阻值,从而改变陷波频率。

// 示例:通过I2C控制数字电位器

void set_notch_frequency(float freq) {

float R = 1.0 / (2 * M_PI * freq * C); // 根据频率计算所需电阻值

uint8_t value = map(R, 0, MAX_RESISTANCE, 0, 255); // 映射为8位值

write_i2c_register(DIGITAL_POT_I2C_ADDR, value);

}

代码逻辑分析

-

freq为期望的陷波频率。 - 根据公式 $ R = frac{1}{2pi f C} $ 计算所需电阻值。

-

map函数将模拟值映射为数字电位器支持的8位值。 - 最终通过I2C接口写入到电位器芯片。

2. DDS(直接数字频率合成)控制

DDS芯片(如AD9833)可生成高精度的正弦波,用于控制压控振荡器(VCO),从而动态调整陷波频率。

3. FPGA控制

在高端设备中,使用FPGA实现陷波频率的实时调节与滤波器参数优化,提升系统的动态响应能力。

5.2.2 自适应陷波技术的发展趋势

自适应陷波器(Adaptive Notch Filter)是一种能够根据输入信号实时调整陷波频率和深度的滤波器结构,适用于多变环境下的ECG信号处理。

LMS算法实现自适应陷波

最小均方误差(LMS)算法是一种常见的自适应滤波算法,其核心思想是通过不断调整滤波器系数,使得输出误差最小。

% MATLAB代码:使用LMS算法实现自适应陷波

mu = 0.01; % 步长因子

N = 1000; % 数据长度

x = sin(2*pi*50*(0:N-1)/Fs); % 50Hz干扰

d = ecg_signal + x; % 带干扰的ECG信号

w = zeros(1, 10); % 初始化滤波器系数

y = zeros(1, N); % 输出

e = zeros(1, N); % 误差

for n = 1:N

u = [sin(2*pi*50*n/Fs), cos(2*pi*50*n/Fs)]; % 输入特征向量

y(n) = w * u';

e(n) = d(n) - y(n);

w = w + mu * e(n) * u;

end

代码逻辑分析

-

mu为学习率,控制更新速度。 -

x为模拟的50Hz干扰信号。 -

d为叠加了干扰的ECG信号。 -

u为输入特征向量,包含正弦和余弦项。 -

w为滤波器系数,通过LMS算法不断更新。 -

e为误差信号,最终得到的e即为去除干扰后的ECG信号。

该算法在实际应用中可以自动跟踪电网频率变化,实现自适应抑制,具有很高的鲁棒性。

尽管陷波器在理论上可以有效抑制特定频率干扰,但在实际工程中仍面临诸多挑战。

5.3.1 频率漂移与温度稳定性问题

由于环境温度变化、元件老化等因素,陷波频率可能偏离设定值,导致抑制效果下降。

解决方案

- 使用 温度系数低的元件 (如PTC、NTC补偿电阻);

- 在系统中加入 自动校准模块 ,定期检测并调整陷波频率;

- 采用 软件补偿算法 ,通过采集噪声频谱自动调整滤波器参数。

热漂移对陷波频率的影响

从表中可以看出,即使是微小的温度变化也会对陷波频率产生明显影响,因此在高精度ECG系统中,必须考虑温度补偿机制。

5.3.2 多干扰源并存下的滤波器协同设计

在某些复杂环境中,除了50/60Hz主频干扰外,还可能存在其谐波(100Hz、150Hz等)以及其他设备引起的干扰(如肌电干扰、运动伪影)。

多频陷波器设计

可以设计多个陷波器并联使用,分别抑制50Hz、100Hz、150Hz等干扰信号。例如:

Input --> [50Hz陷波] --> [100Hz陷波] --> [150Hz陷波] --> Output

滤波器级联的稳定性问题

多个滤波器级联使用时,可能会引起相位失真和系统不稳定。为此,可以采用以下策略:

- 使用 零相位滤波器结构 (如Butterworth滤波器);

- 引入 反馈补偿机制 ,通过数字信号处理修正相位;

- 在PCB布局中优化信号路径,减少寄生电容和电感的影响。

多干扰源滤波器协同设计流程图

graph TD

A[原始ECG信号] --> B{干扰检测}

B -->|50Hz| C[50Hz陷波]

B -->|100Hz| D[100Hz陷波]

B -->|150Hz| E[150Hz陷波]

C --> F[信号合并]

D --> F

E --> F

F --> G[输出干净ECG信号]

该流程图展示了多干扰源情况下的滤波器协同设计策略,通过实时检测干扰频率并动态启用相应滤波器,可以实现高效、灵活的噪声抑制。

本章深入探讨了陷波电路的基本结构、有源滤波技术的应用、数字控制与模拟实现的结合方式,以及在实际工程中面临的挑战与解决方案。通过这些内容,读者可以全面掌握陷波滤波器在ECG系统中的设计方法与优化策略,为后续电路系统集成打下坚实基础。

6.1.1 从电极到输出的信号处理链路

心电图(ECG)信号的采集和处理是一个复杂的系统工程,其核心在于将人体微弱的心电信号从电极采集端,经过一系列模拟电路处理,最终输出到显示或采集系统。整个信号链包括以下几个关键环节:

- 电极接口电路 :这是信号链的最前端,负责将人体表面的生物电信号采集下来。电极通常采用银/氯化银(Ag/AgCl)材质,具有良好的导电性和稳定性。

- 前置放大器 :由于ECG信号非常微弱(通常在0.1mV到5mV之间),前置放大器需要具备高增益、高输入阻抗和低噪声的特性。

- 右腿驱动电路(RLD) :用于抑制共模干扰,提高共模抑制比(CMRR)。

- 滤波器电路 :用于去除ECG信号中不需要的噪声和干扰,包括低通滤波器、高通滤波器以及50/60Hz陷波器。

- 后级放大器 :在信号经过滤波后进行进一步放大,使其达到ADC或显示设备所需的幅度范围。

- 输出接口电路 :将模拟信号输出至后续的ADC或显示系统,有时还包含缓冲放大器以驱动负载。

整个信号链的结构如下图所示:

graph TD

A[电极] --> B(前置放大器)

B --> C{右腿驱动电路}

C --> D[滤波器]

D --> E[后级放大器]

E --> F[输出接口]

6.1.2 各模块之间的匹配与级联设计

为了确保信号在各模块之间传输时不发生失真或衰减,必须注意以下几点:

- 阻抗匹配 :每一级电路的输出阻抗应远小于下一级的输入阻抗,通常遵循1/10规则,以减少电压衰减。

- 增益分配 :由于前置放大器的增益过高会引入噪声,一般采用两级放大结构,前置放大器负责主要增益,后级放大器用于微调和最终输出。

- 电源供电 :所有放大器和滤波器模块需要稳定的电源供电,通常采用双电源(±Vcc)供电方式,以保证信号在0V附近对称放大。

- 接地与屏蔽 :为防止电磁干扰,所有模拟电路应采用单点接地,并使用金属屏蔽罩保护关键电路。

下面是一个典型的心电模拟信号处理链的参数匹配表:

通过上述结构设计和参数匹配,可以有效提升ECG信号的信噪比和稳定性,确保采集信号的准确性和可靠性。

6.2.1 运算放大器与滤波电容的选型标准

在心电模拟电路中,运算放大器是最关键的元器件之一。其选型需满足以下条件:

- 低噪声 :ECG信号极其微弱,因此运算放大器的输入电压噪声密度应小于10nV/√Hz。

- 高共模抑制比(CMRR) :至少应达到80dB以上,以抑制共模干扰。

- 高输入阻抗 :通常要求大于100MΩ,以减少对生物信号的加载效应。

- 低失调电压与温漂 :失调电压应小于100μV,温漂小于1μV/°C,以确保长期稳定性。

- 轨到轨输出(Rail-to-Rail) :便于在低电压供电时获得最大动态范围。

常用的仪表放大器芯片包括:

- AD620 (Analog Devices):低成本、高精度仪表放大器,CMRR高达100dB,增益可调。

- INA118 (Texas Instruments):高输入阻抗、低功耗,适用于电池供电设备。

- LTC6078 (Analog Devices):超低噪声、高带宽,适用于高精度医疗设备。

滤波电容的选择则需考虑其频率响应特性与温度稳定性。常用电容类型包括:

- 陶瓷电容(C0G/NP0) :适用于高精度滤波,具有良好的温度稳定性。

- 聚酯电容(Mylar) :适用于中频滤波,成本较低。

- 电解电容 :适用于低频高容量滤波,但需注意极性。

6.2.2 电阻精度与温漂对系统稳定性的影响

在模拟电路中,电阻的精度和温漂直接影响系统的稳定性和信号的准确性。特别是在前置放大器和滤波器中,电阻值的微小变化都会导致增益误差和频率偏移。

电阻选型标准:

- 精度 :用于放大器反馈和滤波网络的电阻应选择1%或更高精度(如0.1%)。

- 温漂(TCR) :一般要求TCR小于100ppm/°C,以避免温度变化引起的增益漂移。

- 功率额定值 :根据电流大小选择适当的功率,通常使用1/8W或1/4W电阻。

示例:滤波器中的RC网络设计

以一个一阶RC低通滤波器为例,其截止频率为:

f_c = frac{1}{2pi RC}

若选用R = 10kΩ(±0.1%,TCR=25ppm/°C),C = 100nF(NP0型陶瓷电容),则:

f_c = frac{1}{2pi imes 10^4 imes 100 imes 10^{-9}} approx 159Hz

代码示例:使用Python计算截止频率

import math

R = 10000 # 10kΩ

C = 100e-9 # 100nF

fc = 1 / (2 * math.pi * R * C)

print(f"截止频率 fc = {fc:.2f} Hz")

逐行分析:

- 第1行:导入数学库以使用π常数。

- 第2-3行:定义电阻和电容的数值。

- 第5行:代入公式计算截止频率。

- 第6行:输出结果,保留两位小数。

逻辑说明:

该程序用于计算RC低通滤波器的截止频率,确保设计值与实际值一致。通过使用高精度电阻和低温漂电容,可以保证在不同环境温度下,滤波器的截止频率不会发生显著偏移。

6.3.1 信号完整性与失真度的测量

信号完整性是衡量ECG模拟电路性能的重要指标。主要包括:

- 幅值误差 :实际输出信号与理论值的偏差。

- 相位失真 :信号通过电路后产生的相位延迟。

- 谐波失真(THD) :由于非线性元件引入的谐波分量。

测试方法:

- 使用标准信号源 :输入一个已知幅值和频率的标准正弦波信号(如1mV、1Hz)。

- 示波器测量 :观察输出波形,记录其幅值、失真情况。

- FFT分析 :使用示波器或频谱仪对输出信号进行快速傅里叶变换,分析其频谱成分。

测试指标示例:

6.3.2 动态范围与输入输出阻抗匹配测试

动态范围指的是电路在不失真的前提下所能处理的最大信号幅值与最小信号幅值之比。对于ECG系统来说,动态范围应覆盖0.1mV至5mV的输入信号,并能输出0.1V至5V的模拟电压。

测试方法:

- 逐步增加输入信号幅值 ,观察输出波形是否出现削波或失真。

- 测量输入输出阻抗 :

- 输入阻抗:使用信号源与分压法测量。

- 输出阻抗:使用负载法测量。

阻抗匹配测试表:

6.3.3 整体系统的抗干扰能力评估

ECG信号易受多种干扰影响,包括工频干扰(50/60Hz)、肌电干扰、运动伪影等。评估系统的抗干扰能力包括:

- 信噪比(SNR) :衡量信号与噪声的强度比。

- 共模抑制比(CMRR) :衡量系统对共模干扰的抑制能力。

- 陷波器效果 :是否有效抑制50/60Hz干扰。

抗干扰测试流程:

- 在标准ECG信号中加入50Hz干扰信号。

- 测量输出信号的SNR。

- 使用陷波器后再次测量SNR,评估其改善效果。

测试结果对比表:

通过上述测试,可以全面评估心电仪模拟电路的整体性能,确保其在实际应用中具备高稳定性与高可靠性。

心电图(ECG)是临床中最常见的心脏电生理检测手段之一,广泛用于心脏病的筛查、诊断与监测。根据使用场景的不同,ECG设备主要分为静态心电图仪和动态心电监测设备(Holter)两大类。

7.1.1 静态心电图与动态心电监测的区别

静态心电图仪通常用于医院环境,能够提供高精度的心电波形;而Holter设备则更注重长时间的数据采集与存储能力,适用于捕捉偶发性心律异常。

7.1.2 移动式与便携式心电设备的发展趋势

随着可穿戴设备与远程医疗的发展,移动式和便携式心电仪(如Apple Watch、KardiaMobile等)逐渐进入市场。这类设备通常采用低功耗模拟前端(AFE)芯片,配合微型电极实现心电采集。其核心模拟电路设计需要兼顾:

- 低功耗设计 :延长电池寿命;

- 高集成度 :减少PCB面积;

- 抗干扰能力 :适应复杂电磁环境;

- 用户友好性 :简化操作流程。

在实际医疗场景中,心电仪模拟电路不仅要满足基本的信号采集需求,还需应对功耗、干扰、稳定性等挑战。

7.2.1 系统功耗与电池供电方案设计

在便携式设备中,降低功耗是设计的核心目标之一。以下是一些优化策略:

// 示例:低功耗AFE芯片配置(以TI ADS1298为例)

void configure_low_power_mode() {

write_register(CONFIG1, 0x02); // 设置采样率为125 SPS

write_register(CONFIG2, 0x00); // 关闭内部导联检测

write_register(CONFIG3, 0x01); // 使用内部参考电压

}

- 采样率控制 :合理设置采样率,避免过高采样造成不必要的功耗浪费;

- 时钟管理 :关闭未使用的模块时钟;

- 电源管理 :使用LDO或DC-DC转换器优化供电效率;

- 休眠机制 :在无采集任务时进入休眠模式。

7.2.2 电磁干扰(EMI)防护与屏蔽设计

EMI是影响ECG信号质量的重要因素,尤其在医院环境中,各种医疗设备、电源线等都会引入干扰。

优化措施包括:

- 屏蔽电缆与电极设计 :使用屏蔽电缆连接电极,减少电磁耦合;

- 右腿驱动电路(RLD) :将共模干扰反馈回患者身体,形成负反馈;

- PCB布局优化 :敏感模拟电路远离数字电路,使用地平面隔离;

- 滤波器设计 :增加50Hz/60Hz陷波器与低通滤波器,提升抗干扰能力。

随着数字信号处理(DSP)技术的发展,模拟前端(AFE)与数字系统的协同优化成为提升ECG设备性能的重要方向。

7.3.1 模拟前端(AFE)与ADC的接口设计

AFE芯片(如TI ADS1298、ADI ADAS1000)集成了前置放大器、滤波器与ADC,是现代ECG设备的关键组件。其接口设计需注意:

graph TD

A[电极] --> B(前置放大器)

B --> C(滤波器)

C --> D(ADC)

D --> E[数字信号处理器DSP]

- 匹配ADC输入范围 :确保AFE输出电压在ADC输入范围内;

- 时钟同步 :保证ADC采样时钟与主控MCU同步;

- 电源去耦 :为AFE和ADC提供干净的电源,避免噪声引入;

- 阻抗匹配 :在模拟输出与ADC输入之间添加缓冲器(如电压跟随器)。

7.3.2 模拟信号处理与后续数字滤波的协同优化

虽然模拟滤波可以去除大部分噪声,但数字滤波仍不可或缺。常见的协同优化策略包括:

- 模拟预滤波 + 数字后滤波 :模拟滤波抑制高频噪声,数字滤波进行精细处理;

- 自适应滤波 :结合数字算法实时调整滤波参数;

- 小波变换 :用于非平稳信号的特征提取与去噪;

- AI辅助滤波 :如使用神经网络识别并去除肌电干扰。

7.4.1 高集成度IC与模块化设计趋势

未来ECG模拟电路将向更高集成度发展,典型趋势包括:

- 单芯片解决方案 :如SoC集成AFE、ADC、DSP;

- 无线ECG模块 :集成蓝牙/BLE传输功能;

- 多通道集成 :支持12导联心电采集的单芯片;

- 低功耗+小尺寸 :适用于可穿戴设备。

7.4.2 智能化与AI辅助信号预处理的前景展望

AI技术的引入将使ECG信号处理更加智能化,例如:

- 自动识别异常波形 :如室性早搏、房颤等;

- 噪声分类与自适应滤波 :根据环境自动选择滤波策略;

- 远程诊断支持 :通过AI辅助分析,提供初步诊断建议;

- 个性化校准 :根据用户生理特征动态调整电路参数。

这些趋势不仅提升了设备的智能化水平,也为远程医疗和家庭健康监测提供了技术支撑。

本文还有配套的精品资源,点击获取

简介:心电仪模拟电路资料是电子工程与生物医学工程领域的重要内容,主要涵盖心电信号的采集、处理与分析。心电图(ECG)通过模拟电路获取心脏电信号,其质量取决于前置放大器、低通滤波器和陷波电路的设计。本资料包含两份PDF文件,详细介绍了简易心电图仪的结构与实现方法,并深入解析了滤波与陷波电路的设计技术,适用于医疗设备开发、电子工程实践及生物医学教学。

本文还有配套的精品资源,点击获取

相关推荐

- 缝伤口怎么打结三角巾包扎法-临床医师技能考试

- 缝伤口怎么打结2023年临床执业医师技能操作考官提问解答-急救板块

- 绽媄娅的产品怎么样这些国产老牌是“赔钱货”吧!爆炸好用却没人知道~

- 绽媄娅的产品怎么样解码易敏人群抗老难题,绽媄娅再造爆款单品

- 绽媄娅的产品怎么样蜜蜂6月2日(晚场零食节)直播预告清单

- 绽媄娅的产品怎么样背靠生物医用材料商的护肤品牌绽美娅在618中突围而出

- 绽媄娅的产品怎么样美妆节:水乳水霜、精华水、护肤套组!

- 绽媄娅的产品怎么样绽媄娅:以医学态度研发护肤品 以创新功效为提升用户体验

- 绽媄娅的产品怎么样绽媄娅纳金肽精华28天真人测试 多维抗老媲美医美

- 绽媄娅的产品怎么样绽媄娅纳金肽淡纹小金瓶开箱:黑科技加持 涂抹式抗老神器