医疗探针怎么做芯片法律知识教程

作者 吴国平 北京市隆安律师事务所

“芯片技术与法律的融合”是芯片行业法律服务的关键,因为芯片行业技术高度复杂且技术迭代迅速,律师不仅需要掌握传统的法律知识,还必须对芯片设计、制造流程、知识产权等技术方面有深入的理解,才能为客户提供精准有效的法律支持。

帮助律师理解芯片制造的基本原理和工艺流程,便于为客户提供更为精准的法律咨询服务。

提高律师在芯片知识产权,例如专利、版权特别是关于芯片生产工艺相关的商业秘密保护等方面的法律服务能力,增加芯片技术背景和法律知识的融合度。

了解芯片行业供应链管理的复杂性,增强律师在处理合同、技术转让、跨国交易时的合规风险应对能力。

芯片技术涉及微电子制造、材料力学、物理电子学、半导体物理、机械力学、计算机和法学,法学知识只是其中很小的学科,需要了解交叉学科的基础知识,才能融通并支持法律学科的作用。

1. 法律服务的技术复杂性

芯片行业涉及的技术领域包括半导体材料、纳米制造、光刻工艺、晶圆封装等,每一项技术都可能涉及到专利保护、技术转让和商业秘密等问题。因此,律师需要具备对这些复杂技术的基本理解,以便在商业秘密保护、侵权纠纷和商业合同中提出恰当的法律意见。

例如,2008年,英特尔起诉其前高管Fran?ois Piedno?l,指控他在离职后加入竞争对手AMD时,非法带走了数百份敏感文件,其中包括了英特尔的处理器设计文件。对技术文件的理解是法律判断的基础。

2. 芯片IP保护需要律师对技术的充分理解

在芯片行业,商业秘密和专利诉讼往往是技术复杂度最高的领域之一。芯片公司的核心技术都是通过商业秘密并辅助以技术专利来实现保护的,涵盖从材料创新到制造工艺的各个方面。律师不仅要熟悉知识产权法规,还需要了解技术背景,确保在相关的法律程序中,能够准确理解、描述或解释技术问题。对于知识产权保护而言,技术细节是胜诉的关键。

3. 律师审查芯片技术合同需要技术背景才能涵盖所有风险

芯片企业经常进行技术合作、技术许可和技术转让。这些交易中,合同条款往往会涉及技术细节,如技术机密的保护、技术转让范围、许可使用限制等。如果律师对这些技术不了解,就难以确保合同条款能够覆盖所有技术风险。

举例来说,芯片代工协议中,往往会涉及到特定的生产工艺、质量控制标准以及知识产权归属问题。律师在起草合同时,必须对这些技术条款的技术细节有充分的理解,然后才能进行严格把关,以确保客户的技术和商业利益得到全面保护。

4. 律师与技术专家的协作和交流需要基础的行业知识

在芯片行业,律师与技术专家的紧密协作是不可或缺的,但是交流的前提是需要律师对芯片行业基础知识有充分的了解。律师在处理技术相关的法律事务时,往往需要聘请工程师或技术专家作为顾问,以便更好地理解并解释技术细节。这种技术与法律的协作关系不仅帮助律师更好地处理案件,也帮助技术专家以法律语言来表达他们的技术观点。

5. 芯片行业中的新兴技术挑战

随着技术的不断进步,诸如量子计算、光子芯片等新兴技术不断涌现,这给律师带来了新的挑战和机遇。新技术领域的法律规范尚未完全明确,因此律师需要在这些新领域中不断学习,提前为客户规避可能的法律风险。例如,量子芯片的研发涉及到全新的技术架构和物理原理,这些新兴技术尚未在现行法律体系中完全涵盖,律师需要与行业技术专家保持密切合作,确保技术创新在法律框架内合法进行,同时为未来的法律诉讼打下基础。

在芯片行业,技术与法律的融合是不可或缺的。律师不仅要精通法律,还必须对半导体行业的核心技术有基础理解,才能为客户提供全面有效的法律服务。这种对交叉学科的掌握和融合能力不仅帮助律师在知识产权、技术合同、国际纠纷等领域中获得优势,也将随着技术的不断进步,成为未来法律服务的关键要素。

随着中国芯片设计、制造和应用等核心技术的提升,知识产权(包括专利、商标、商业秘密等)诉讼在未来几年将大幅增加。特别是中国芯片企业逐步在国际市场上崭露头角后,不可避免地会产生涉及知识产权的纠纷,既有中国芯片企业对境外企业侵权行为的诉讼,也会有境外企业对中国企业提起的诉讼。这类诉讼的复杂性主要体现在法律适用和技术细节方面。

随着市场集中度的提升,中国芯片领域的企业之间竞争日趋激烈,高端技术人员的争夺将不可避免。西方企业可能会担心中国企业通过高端人才的跳槽等方式在芯片市场上获得竞争优势,而提起相关诉讼。同时,中国大陆企业之间也存在高端技术人员离职引发的商业秘密泄露风险。

由于西方企业在中国设立的合资企业或者技术转让协议可能涉及大量的技术共享,围绕技术授权、知识产权归属、以及合同执行等方面的纠纷可能会激增。这类案件往往需要兼顾跨国合同法和中国本土法律的双重要求,对合同条款的解读、技术的界定以及专利的归属提出了更高的法律能力要求。

未来芯片产业相关的法律诉讼,必然要求大陆律师具备更专业和综合的知识储备。具体而言,中国大陆律师需要在以下方面做出提升:

技术理解与跨学科能力

芯片诉讼涉及高度专业化的技术知识,律师不仅需要精通相关的法律,还需要对芯片设计、制造和应用的基本技术流程有深入了解。这就要求律师具备跨学科的能力,甚至需要科技和法律的复合型知识背景,能够准确解读技术文件和专利说明,从而在诉讼中具有说服力。

* 国际法律事务能力

中国律师在处理芯片领域国际纠纷时,需要具备良好的国际法律事务能力,包括对跨境诉讼、国际仲裁规则的理解,熟悉海外市场的法律环境,甚至具备涉外沟通和谈判的能力。这对于帮助客户解决跨境纠纷,特别是在知识产权和技术转让领域的诉讼中至关重要。

* 专业的合规与风险管理能力

在知识产权保护日益严格的趋势下,律师需要熟悉国内外的知识产权保护标准,帮助企业建立完善的知识产权保护和管理体系,避免侵犯他人的专利和商业秘密。同时,也需要帮助企业防范反垄断、数据合规等方面的风险,确保在商业合作和技术转让中的合法性。

* 敏锐的政策理解与前瞻性

由于中国大陆在芯片领域的产业政策和法律制度可能会随时调整,律师需要时刻关注国家相关政策动向并保持前瞻性。对于法律服务领域,政策的解读不仅仅局限于当前的法律条文,还要对未来可能出台的法规或政策调整进行预判,确保为企业提供具有前瞻性的法律建议。

* 争议解决的灵活性与创新能力

在芯片领域的诉讼中,律师可能需要更多地参与到和解、仲裁等争议解决的环节,以实现企业利益最大化。尤其是在中国大陆和外国企业合作的案件中,律师需要帮助客户通过灵活的谈判策略和创新的争议解决手段,降低法律风险和诉讼成本。

芯片的发明可以追溯到20世纪中期。德州仪器(Texas Instruments)在1958年发明了第一个集成电路,最早的设计用途之一是为军事导弹制导系统提供精准计算。1962年,德州仪器为“民兵-I”型和“民兵-II”型导弹制导系统研制22套集成电路。军事上的需求成为了半导体技术突破的主要驱动力。例如,美国宇航局和国防部为导弹、雷达系统的芯片开发提供了大量资金,这些需求推动了早期集成电路的研究与生产。

1958 年美国创建了先进研究计划局(ARPA),1972 年更名为美国国防高级研究计划局(DARPA)。DARPA 的宗旨就是开展 “改变游戏规则”的高风险、高回报技术研发,“避免技术突袭并谋求对对手的技术突袭”, 并邀请麻省理工学院约瑟夫·利克理德(JCR. Licklider)教授出任首任主任。美苏军备竞赛是这段时期芯片发展的核心动力。为了保持战略优势,美国政府通过DARPA等机构大量投资芯片研发。这些资金促进了更高性能、更小尺寸、更可靠的芯片诞生,也为后来的商用电子产品奠定了基础。

美国国防高级研究计划局官网“Create Technological Surprise for National Security”

在20世纪70年代,军事应用对芯片的要求更高,推动了集成电路(IC)的进一步发展。微处理器成为战斗机、弹道导弹防御系统、卫星等关键军事设备的核心组件。

进入21世纪,芯片技术已经发展到纳米尺度,军方对高性能计算和人工智能(AI)芯片的需求日益增长。当前,芯片在军事领域的主要应用包括无人机与自动化武器系统、导弹防御与打击系统、网络战与信息安全、军事卫星,从具体应用来看,加密芯片和安全处理器用于防御网络攻击和确保军事通信的安全性、AI芯片用于无人机的导航、侦察和自动决策、高性能芯片用于导弹制导系统、目标识别和跟踪。

各国为了提高军事自主权,开始设计定制化的军事芯片,减少对外部供应链的依赖。这意味着未来在军事芯片领域,国家之间的竞争将更加激烈,涉及到尖端技术的研发和国防工业的供应链布局。美国国防部国防研究与工程局负责人声称:五角大楼希望通过加大投资力度,确保将关键供应链带回美国,减少对外依赖。即便无法保证美军所需的微电子元器件完全由美国工厂生产,也得找到可信任的代工厂,避免出现后门隐患。

芯片的技术差距同时也是中国芯片法律服务的差距

一个国家的某个行业(例如芯片或者人工智能项目)刚刚起步或仍处于发展初期时,法律服务也相对其他国家较为滞后,同时往往跟不上自己国家芯片行业的发展速度。中国的芯片行业在过去几十年中经历了快速的发展,但相对来说,行业的法律服务体系建设可能还没有成熟。这种滞后主要是因为法律服务往往依赖于行业的实际需求,而芯片行业的发展和技术创新通常会超前于法律服务的完善。

芯片行业的法律服务需求通常随着芯片行业的成熟而增加。相对于美国的芯片行业发展,技术差距同时导致了法律服务的差距,目前中国芯片企业的法律需求可能主要集中在基础的合同、公司治理等方面。随着中国芯片行业的快速发展和复杂化,商业秘密保护、专利纠纷等复杂法律问题开始涌现,相应的法律服务需求也会随之产生。这些需求推动了法律服务水平的提升,但由于科技发展速度较快,法律服务水平可能在短期内难以完全跟上。反过来,高水平的法律服务可以为中国芯片行业的科技创新提供保护和支持。最重要的就是通过知识产权保护,律师可以帮助芯片公司保护其核心技术,避免被竞争对手复制和侵权。此外,法律服务还可以在跨境合作、并购、融资等方面为芯片企业提供支持,推动行业的进一步发展。

但是,从整体上来说,因为芯片行业涉及高度复杂的技术和专业知识,中国的法律服务人员没有跨学科的背景,缺乏对包括芯片设计、芯片生产工艺、封装、商业秘密、国际贸易等领域的法律知识以及对芯片技术的深入理解。在中国,具备这种跨领域能力的法律人才相对匮乏,导致中国芯片行业的法律服务水平相对于国外仍有较大的差距。

中国芯片行业的快速发展是近十几年的事情,而在法律领域,尤其是高科技领域的法律服务,需要长期的实践和经验积累。与美国相比,中国的律师在处理涉及高科技和芯片的复杂法律问题时,缺乏足够的案例和经验。

在芯片企业内部,因为外资方在海外聘用的惯性,在中国大陆的运营过程中也会聘请在海外执业的律师或者专业顾问(没有律师执照)作为In-house Counsel(IC),IC通常具备较强的技术背景,深入了解芯片设计、制造和知识产权等相关领域的技术细节。这使他们在处理芯片公司内部法律事务时具有明显的优势,例如制定知识产权策略、合同审查、内部合规管理等。

相对于中国大陆的律师,尽管IC具备丰富的技术知识,但他们往往缺乏在中国大陆实战的庭审经验,对中国的司法环境和司法实践缺少了解,同时中国法律规定外国律师不能在中国出庭,所以芯片公司的IC角色更多是咨询和合规管理,较少参与在中国大陆的实际诉讼过程。这种局限导致在面对复杂的诉讼案件时,IC无法独立有效地应对。

中国本地的律师通常具有丰富的庭审经验,熟悉中国的法律程序和司法系统。他们在诉讼、调解、仲裁等法律程序中表现出色,能够有效地应对挑战。但是,相对于IC来讲,由于芯片行业的高技术门槛,这些出庭律师可能缺乏对芯片技术的深入理解。在诉讼中,涉及复杂的技术问题时,本地律师可能难以准确把握技术细节,从而影响案件的质量。

在芯片法律服务市场中,IC与本地律师之间的合作是十分必要的。这种合作可以克服技术与法律之间信息传递不畅的问题。但是,这样的合作仍需中国本地既懂技术又精通法律的跨学科律师,在整体芯片法律服务市场上的这种复合型人才仍然稀缺。

中国政府因为法律主权和法律市场的保护政策,限制了海外律师参与中国大陆诉讼的活动,当然,因为诉讼过程是高度对抗的活动,需要对汉语有高度熟练的掌握,这对于国外律师来说是天然的壁垒,作为国际化的深度需求,应当探讨在部分领域放开对执业领域的限制,如知识产权争议中,应当试点允许国外律师与本地律师共同出庭或以顾问身份直接参与法院诉讼活动。国际化的合作对本土律师的业务能力提升本身就是非常好的契机,并以此通过知识产权领域为开端稳步开放,实现法律主权、市场保护和国际化的平衡。

电子设计自动化(EDA)工具是芯片设计过程中不可或缺的工具,用于从逻辑设计到物理设计再到验证的每个阶段。全球EDA市场由几家主要厂商主导,它们提供的软件在功能和应用范围上各具特色。

中国芯片公司严重依赖海外专业公司提供的先进电子设计自动化 (EDA) 软件、可重复使用的架构构建块(称为 IP 核)和外包设计服务。 Synopsys、Cadence 和 Mentor几乎控制着中国 80% 的市场份额,如果考虑台积电的尖端工艺技术上述比例可能更高 。

律师需要理解这些工具的市场状况、授权方式和收费模式,以便为使用这些工具的企业提供更好的法律咨询服务,特别是与软件许可、知识产权和合同管理相关的问题。

Synopsys是全球最大的EDA工具供应商之一,总部位于美国加利福尼亚。它提供一系列广泛的EDA工具,涵盖了芯片设计的各个阶段,包括设计、验证和分析。

主要产品为Design Compiler:用于逻辑综合,将高层次的设计描述转换为门级网表,是后续物理设计的基础。PrimeTime:用于时序分析,确保芯片的信号在规定的时间内到达目标。VCS:主要用于功能仿真和验证。IC Compiler II:用于布局布线,是后端物理设计的重要工具。

Synopsys授权与收费模式:

Synopsys 的工具一般采用年度许可授权(annual license),分为节点锁定许可(node-locked)和浮动许可(floating license)。其中节点锁定许可限定软件只能在特定计算机或节点上使用,适合小型团队。浮动许可是指软件可以在指定数量的用户之间共享许可,更适合大型团队。

Synopsys的收费模式主要包括一次性软件许可费以及按年支付的维护费,通常根据使用的工具、许可的用户数和许可的功能模块来定价。

Cadence 也是全球领先的EDA工具提供商,总部位于美国加利福尼亚。该公司在芯片设计和验证工具领域具有强大的市场影响力,尤其在模拟和数字设计方面的工具得到了广泛应用。主要产品为Virtuoso:专注于模拟和混合信号电路设计,提供从电路设计到物理布局的一站式工具;Innovus:一个数字布局布线工具,具有高性能和低功耗的优化功能。Spectre:用于模拟电路的仿真,特别适用于高精度的模拟信号仿真;Xcelium:功能验证工具,用于芯片设计中的大规模验证。

Cadence授权与收费模式:

Cadence 的软件授权模式与Synopsys 类似,提供节点锁定许可和浮动许可,也有按项目需求的短期许可(project-based license)。

Cadence收费模式:通常为年度订阅模式,费用与工具的复杂程度和用户数量挂钩。Cadence 还提供基于用量的许可模式,允许客户按实际使用时间付费,这对于小型项目或短期使用尤为合适。

Mentor Graphics 是另一家知名的EDA公司,2017年被西门子收购后更名为Siemens EDA。该公司在PCB设计和验证、数字和模拟电路设计等方面具有较强的市场竞争力。

Mentor Graphics主要产品包括Calibre:最著名的物理验证工具之一,广泛用于芯片制造工艺的设计规则检查(DRC)和参数提取(LPE);PADS:主要用于印刷电路板(PCB)设计,适用于中小型企业;ModelSim:功能强大的仿真工具,支持混合信号仿真,广泛应用于FPGA和ASIC设计中。Tessent:设计为测试(DFT)工具,帮助设计人员进行芯片可测性设计和测试生成。

Mentor Graphics授权与收费模式:

西门子EDA也提供节点锁定许可和浮动许可。此外,西门子还根据客户需求提供定制化的企业许可协议(enterprise license agreement),适合大型客户。

Mentor Graphics收费模式:西门子EDA的收费模式较为灵活,包括年度订阅、用量许可和永久许可(perpetual license)。永久许可通常伴随着年度的维护费用,以便客户获得最新的软件更新和技术支持。

Ansys是一家专注于多物理场仿真的公司,近年来进入EDA领域,特别是在电磁兼容性(EMC)和电磁仿真(EM simulation)方面有着广泛应用。

Ansys的主要产品为Ansys HFSS:专注于电磁场仿真,广泛用于射频(RF)和高频电路设计中;Ansys RedHawk:主要用于电源完整性分析,确保芯片的电源分配网络在高性能和低功耗应用中稳定工作。

Ansys的授权与收费模式:

Ansys 提供浮动许可和云许可。浮动许可允许多个用户在不同的地点共享使用,而云许可则允许用户通过云计算平台灵活访问工具。

Ansys的收费模式包括年度许可和基于云使用的按需收费,按计算资源和使用时间计费,非常适合需要高计算能力的仿真任务。

其他EDA工具

Keysight Technologies:提供的ADS(Advanced Design System)和GoldenGate工具主要用于射频和微波电路的设计和仿真。

Xilinx(现被AMD收购):提供专门用于FPGA设计的工具,如Vivado,广泛用于可编程逻辑器件的设计。

软件授权合同许可范围:律师需帮助客户仔细审查许可协议中的使用范围,确保工具的使用不超出许可限制,如节点锁定是否适用于特定地点,浮动许可是否允许全球使用等。

更新与维护条款:EDA软件的更新和技术支持是长期使用的重要部分,合同中应明确维护费用、技术支持响应时间和更新频率等细节。

违反使用条款的后果:如果企业在授权范围外使用EDA工具(如超出ID使用浮动许可),可能会引发合同纠纷或罚款,律师需审查协议中关于违规使用的罚则。

收费模式的法律风险

用量许可与计费准确性:对于按使用时间或计算资源收费的许可模式,确保收费的准确性非常重要。客户应获得透明的使用报告,并确保收费符合合同规定。

永久许可与知识产权归属:永久许可通常伴随着高昂的一次性支付,因此需要明确软件的所有权和知识产权是否归企业所有,特别是在跨国交易或技术转让中。

律师在为EDA工具的采购、使用或许可协议提供法律咨询时,需充分考虑这些授权和收费模式中的法律条款,以确保客户的利益得到最大化的保护。

1、关于用户(被授权人)电脑ID

不同的EDA工具可能使用不同的系统,例如CentOS、OpenSuse、Ubuntu和Windows,并非所有操作系统都支持所有用户ID 类型,因此部分系统用户可能需要单独下载EDA厂家的主机许可管理 ID工具用于唯一标识用户的设计工具或 IP 获得许可的机器。通常情况下,主机 ID 类型取值于 MAC 地址、硬盘驱动器序列号、加密狗 ID 。

2、floating license(浮动许可证)。

浮动许可证基于许可证服务器进行管理。许可证服务器运行在被授权人公司内部的某个计算机上,负责跟踪和分发软件的使用权。所有用户通过网络访问这个许可证服务器,当某个程序员启动软件时,程序员电脑会向许可证服务器请求一个许可证。当用户关闭软件时,许可证会被归还到许可证池,供服务器分配给其他用户使用。这样,许可证可以在网络中的用户之间动态分配,最大限度地利用资源,减少不必要的许可证浪费。

上述特点适用于跨国公司在不同国家和地区拥有团队,可以通过浮动许可证模式跨时区共享许可证。例如,中国的设计团队在白天使用软件,而美国的团队在亚洲晚上接班使用,从而优化了许可证的利用率。

浮动许可证允许多个用户通过网络共享同一许可证,避免了为每个用户单独购买许可证的高昂成本。但是浮动许可证如果某个时间段内的用户需求超过了许可证池的容量,那么额外的用户可能会被阻止访问EDA软件(需要追加购买),这可能会对工作流程产生影响。另外,由于浮动许可证依赖于许可证服务器的正常运行,如果许可证服务器出现故障或网络连接问题,可能会导致整个团队无法使用EDA软件。

3、node-locked license(节点锁定许可证)

许可方向被许可方发放的节点锁定许可,意味着被许可方允许仅在特定设备上(锁定用户电脑ID)安装和访问EDA软件;一次仅供一名用户使用。节点锁定许可证与被许可方的电脑ID相关。

特定情况比如员工离职、硬盘故障或购买新电脑时,需要被许可方联系EDA厂家以获取替代授权码,以更新先前发布的授权电脑ID。一般需要被许可方证明先前的已发布的授权代码和受其约束的软件已被永久删除或摧毁。

4、distributable component license(可分发组件许可)

可分发组件许可是一种专门用于授权某些可嵌入设计中的IP核(后续章节会有单独介绍)或特定设计功能的许可模式。它通常用于允许被授权人在设计、集成和分发其产品时,合法地使用EDA工具提供的特定设计组件或IP核。这种许可在EDA工具的IP核授权和芯片设计和嵌入式系统设计中比较常见。

IP核是EDA工具公司提供的可重用设计模块,可以嵌入到芯片的设计中,简化开发过程。IP核可以是各种功能模块,比如标准总线接口、存储控制器、处理器内核、加密模块等。通过可分发组件许可,用户能够获得使用这些IP核的合法权利,将其集成到设计中并在特定的项目或产品中分发。例如Synopsys 的 DesignWare IP 是一组可重用的设计组件,用于实现标准协议,如 PCI Express、USB、DDR、以太网等。这些 IP 核经过优化,可以直接集成到 SoC设计中。Cadence 允许用户通过特定的许可模式获取 Tensilica 处理器 IP 的授权,以嵌入到自家设计的 SoC 中,并在市场上分发这些产品。每个项目通常需要单独的许可,许可费用和条款会根据使用的处理器功能和数量不同而变化。

特定的设计功能,例如Synopsys 提供的验证工具中加速器(accelerators)、Cadence 的特殊功能验证和仿真工具,这些工具中的高端功能都需要通过可分发组件许可进行单独授权。

可分发组件许可模式允许芯片设计公司将包含这些组件的设计转授权给客户,甚至嵌入到实际生产的芯片中。但是,授权条款的复杂性和高成本可能会对被授权人带来一定挑战,某些许可只适用于特定的项目或特定产品数量(收费梯度),因此在选择和管理可分发组件许可时,企业需要仔细考虑其长期战略和技术依赖性。

芯片的性能,60%取决于芯片的架构,以ARM指令集授权为例,ARM允许芯片厂商自行设计ARM架构的core,只要与指令集兼容即可。目前获得这种授权方式的公司仅包括高通、华为等几家公司。

core licenses (Built on Cortex, BoC license)

ARM公司向芯片厂商授权已经设计好的IP,包括CPU。芯片厂商可以修改core的配置,但不能修改core本身的设计。联发科、华为等公司就是得到core licenses。

从ARM的产品线看,包含CPU、 NPU、实体IP(Physical IP)、Security IP、System IP,

CPU(实体化的指令集)核来看,包含Cortex-A、Cortex-R、Cortex-M三个大类,GPU核为Mail GPU。

Cortex-A系列处理器是针对高端应用而设计的,通常应用于智能手机、平板电脑、数字电视和网络设备等。这些处理器拥有高性能、大规模的内存管理单元以及大量的内部缓存,支持多核处理和虚拟化技术。Cortex-R系列处理器是针对实时应用而设计的,通常应用于汽车、工业控制和医疗设备等。这些处理器拥有极低的延迟、高精度的计时器和内部存储器保护机制,能够在实时响应和高可靠性方面表现出色。Cortex-M系列处理器是针对低功耗、低成本、嵌入式应用而设计的,通常应用于传感器、智能家居、工业控制和医疗设备等。这些处理器拥有低功耗、小尺寸和低成本等优点,同时也支持实时性、安全性和可靠性等特性。

收费方案:

Arm 目前实施的是user-based licensing (UBL),通过Local License Server (LLS)和Cloud License Server (CLS)实现授权管理。其中Total Access 授权方案,针对大型企业,包含最全面的 Arm 最新技术和工具;Flexible Access 授权方案,适用初创和中小型企业设计的“按需支付”模式,为早期初创企业提供快速、经济、低风险的芯片原型之路。Academic Access 方案,适用学术机构专享会员协议,用户可以随时访问预先设计的 Arm IP 套件以满足不同需求。

以Flexible Access收费模式为例(包含A系列6个Processor、R系列5个Processor、M系列9个Processor),(不包含高阶的Processor)用户需要支付年度费用约21万美元,还需要支付License fee和Royalty(按照项目或者计件)。

授权合同特殊要求:

1、客户设计的芯片必须遵守ARM设定的兼容性标准。ARM可能会要求进行某种形式的测试或认证,以确保最终的芯片设计与ARM指令集保持一致。

2、ARM可能会保留对客户设计过程进行审查的权利,确保知识产权的合理使用以及技术规范的遵守。

3、ARM可能会对申请方的资质和信誉进行合作背景调查,避免与可能侵害其知识产权的企业合作。例如,是否存在非法复制、修改或滥用其指令集架构。

指令集在中国大陆的诉讼案例

根据第三方发布的信息,LoongArch的指令集个别一些指令如maskeqz/masknez 与 MIPS R6 selnez/seleqz、寄存器跳转指令 jirl 与 RISC-V jalr 语义、去除内存寻址的括号记法外的汇编语法等与MIPS 指令集近似,这也是LoongArch指令集与MIPS 指令集纠纷的原因之一,尽管两者在中国大陆的纠纷已经结案(LoongArch胜诉), 但是诉讼过程显示指令集合法授权或自主开发指令集过程中,指令集自主开发者应明确划分指令集独创性的界限。

软核(Soft IP Core)是一种以代码形式(通常是HDL硬件描述语言,如Verilog或VHDL)交付的IP核,具有可移植性高、灵活性强的特点。软核主要用于芯片设计的早期阶段,设计师可以根据需要对其进行修改、定制,并将其集成到整体芯片设计中。因为软核不是固定的硬件结构,用户可以将其合成、优化到目标工艺节点或目标硬件环境。软 IP 通常是不可编辑的,因为源代码经常被锁定,必须作为“黑匣子”在整个项目中实现。商用的IP核使用授权都有严格的许可协议,必须遵守这些协议。AMD等公司提供的设计工具试用期为30天,但是IP核的试用期因为需要进行测试,通常是120天。

软核的特点与优势

可移植性:软核IP并非依赖于特定的制造工艺,因此可以在不同的制造工艺和芯片设计环境中重用。设计团队可以根据目标工艺库(如不同制程、不同厂商的工艺)对软核进行优化,从而实现最佳性能和最小面积。

灵活性:软核IP以源代码形式交付,设计团队可以根据需要调整代码。例如,可以根据芯片性能或功耗要求进行修改,删除不必要的功能模块,或增加特定功能以满足特定应用场景的需求。

便于验证:软核IP通常支持仿真验证,通过使用EDA仿真工具(如ModelSim、Synopsys VCS等)来在不同的工艺节点上进行模拟,确保功能实现的准确性。此外,设计师还可以为软核增加自定义的测试模块,从而进一步确认芯片的可靠性。

适合特定应用的优化:设计师可以根据芯片的实际应用场景,对软核IP进行优化,例如调整数据位宽、改进逻辑路径等,以提升特定功能的性能或降低功耗。这种灵活性使软核适合应用于从通用微控制器到专用处理器等各种场景。

软核的使用过程

配置和调整:设计团队在获得软核后,可根据目标芯片设计需求进行配置,比如调整接口、修改内核参数等,使其更好地匹配最终产品的需求。

逻辑综合(Synthesis):在将软核集成到芯片设计后,使用EDA工具对其进行逻辑综合。逻辑综合过程将HDL代码转化为门级电路,从而适应目标工艺节点的需求。此过程会对代码的逻辑结构进行优化,以在特定硬件上实现最佳性能。

物理设计和流片:综合后的设计进入物理实现阶段,完成芯片布局、布线等工作,最终集成到整个芯片版图中。软核的灵活性使得它可以在物理设计阶段进一步优化,以实现小面积和低功耗。

验证和测试:在整个设计过程完成后,进行完整的验证和测试。软核IP可以通过仿真和FPGA等原型验证环境进行功能验证,确认最终设计的可靠性和性能。

软核的应用场景

软核非常适合中小规模公司或初创公司使用,因为其购买成本通常较低、可根据不同设计需求进行优化,还可以随着项目变化进行调整。

Synopsys提供数千种不同类型的软核IP,涵盖逻辑库,嵌入式存储器,模拟库,有线和无线接口,安全性,嵌入式处理器和子系统等。国际上Arm、Synopsys、M31、Faradya、Cadence和Alphawave等能提供完整的IP。国内IP核厂商包括芯原股份、寒武纪、芯动科技(Innosilicon)、华大九天、锐成芯微、腾芯微。

三大巨头都是通过不断收购经过验证产品的厂家或者竞争者,不断取得竞争优势。巨头的成长之路是充分竞争后不断合并收购的结果,如果没有充分的、分散的、长期的市场竞争,不可能出现单一的优势公司。

1988年,SDA和ECAD两家公司的高层做了一个重大决定。他们决定将公司合并,成立一家新的软件公司,取名叫Cadence。第一任CEO是原SDA的COO,Joe Costello。

1989年进行了一次收购。它收购了一家名叫Tangent Systems的公司(tangent,正切),因为他们有一款基本标准单元和门阵列的布局布线产品,分别叫作Cell 3 Ensemble和Gate Ensemble。基于这两款产品,Cadence将其打造成未来布局布线工具的主心骨。其融合之后的新产品名叫,Silicon Ensemble。

1990年,Cadence收购了Gateway Automation。Gateway当时是Verilog语言和RTL仿真器的发明者,而且还拥有一个非常快速的门级逻辑仿真器,名叫Verilog-XL。

1991年,Cadence收购了Valid公司。这家公司的明星产品Composer模拟版图提取工具,曾广泛应用于门阵列设计和印制电路板(PCB)设计之中。

1998年,Cadence收购了Ambit Design Systems,之后推出了名为BuildGates的逻辑综合工具。而在2003年,Cadence还收购了Get2Chip公司来进一步工具逻辑综合工具。

2001年收购Silicon Perspective。该公司拥有一款名叫First Encounter的芯片布局工具,以及一款叫CadMos的SI分析工具,并为下一代布局布线做好了技术储备。

2002年收购Simplex。该公司的产品将为Cadence补足了寄生参数提取和分析的能力。

2002年收购IBM硬件仿真业务。

2005年收购Verity公司。这家公司开创了一种可约束的随机验证方法学,并为此设计了一款语言,名叫“e”。通过这款设计语言,工程师可以将设计描述进行更高级的抽象。

2010年,Cadence收购了Denali公司,拥有了为Memory建立模型和提供IP的业务。

2013年,Cadence收购Tensilica是当年非常出名的收购案。Tensilica当时是可重构处理器IP的领头羊,其产品可以应用于音频和视频处理等专业领域的处理器中,而且能提供面向不同应用场景和需求的多用途处理器。

2014年,Cadence收购Forte Design Systems,使其拥有了高阶综合工具。它也是Cadence Stratus-HLS的前身。

以上可以看到Cadence在 EDA 领域的领先地位是几十年技术积累、不断收购、用户反馈优化以及大量资本研发投入的结果。EDA 软件本质上是复杂的工具链,涵盖了从芯片设计、验证到制造的各个环节,其核心竞争力体现在长期积累的程序算法,尤其是在物理设计、时序分析、逻辑综合等方面,这些技术都是多年研发、并购、积累、优化的成果。

中国人如果想要开发属于自己的EDA工具,需要庞大的用户基础和用户反馈机制(可以理解为windows系统迭代过程中BUG反馈的重要性),用户在已经有成熟、稳定、可信产品的情况下不会轻易转向初步自研的EDA工具,所以除非在特定场景,例如军用领域,否则在商业化市场中自研的EDA很难有市场和出路,Synopsys 和 Cadence 等公司在全球范围内拥有大量客户,客户的使用反馈推动了他们的持续改进,这种规模效应使他们能够保持行业领先地位。

中国如果试图以行政手段短期取代三巨头的EDA软件,还面临三巨头的知识产权壁垒,这些公司有大量与芯片设计流程相关的专利,构成了技术壁垒,中国很难轻易突破。

中国国产EDA的发展之路,首先需要认清和接受以上现实,不可依靠行政力量拔苗助长,而应该从较简单的部分入手,逐步掌握某些模块(如电路仿真、版图设计、验证等),积累经验和技术,然后逐步向更复杂的整体 EDA 链条发展。考虑到技术更新迭代,这个过程可能需要数年时间,但可以从低到高端逐步形成可替代性,进而蚕食三巨头的优势。另外,尽管商业 EDA 软件具有专利保护,但一些开源项目,如KLayout(https://github.com/klayout/klayout)为中国开发自主 EDA 提供了借鉴的基础。通过利用和优化这些开源工具,可以缩短研发周期,并在此基础上开发更多定制化工具。

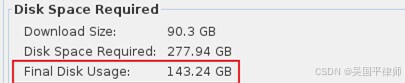

以AMD的VIVADA软件为例,该软件的安装空间如下截图:

EDA的安装包显示其庞大且复杂的代码量,EDA软件通常包含数千万行C++代码,以现有的反编译工具,即使成功反编译,后续理解和分析这些代码所耗费庞大的人力和时间成本,可能比自己开发的成本还要高。

EDA商业软件有巨大的商业价值,任何公司都会采取和商业价值对应的代码混淆、加密和保护技术,使得反编译难度和反编译后的代码难以理解。

芯片产业有自己的产业链条,任何一个公司只是产业环节中的一个节点,任何链条中的公司都依赖于健康的竞争环境,通过合法手段开发自主知识产权是赢得行业信任和客户支持的关键。

商业软件的使用通常受严格的许可协议限制,其中明确禁止用户进行反编译、逆向工程、反汇编等行为。这些协议具有法律效力,违反这些条款会导致严重的法律后果。

1、禁止公布任何基准测试结果

EDA的基准测试,是指通过一系列预设硬件配置以检验一定复杂项目的门级网表合成时间、仿真速度、时序约束精度、功耗等数据,以评估EDA软件在不同设计任务中的性能、效率、稳定性和功能性。基准测试旨在为芯片设计工程师和企业提供有关软件实际表现的可量化信息,帮助他们选择适合自己需求的工具,同时也为EDA厂商评估软件的市场竞争力和优化方向提供依据。

基准测试涉及EDA软件在特定条件下的表现,某些测试方法或结果可能间接泄露厂商的技术细节和优化策略。EDA软件厂家担心公开的基准测试可能无意中揭示某些关键性能指标或算法特性,进而为竞争对手提供参考。所以EDA授权协议中都明确表述禁止用户公布任何基准测试结果。

2、技术出口规定。(本条详见后续芯片技术管制章节)

3、EDA软件在自动驾驶和医疗设备领域的责任排除

EDA软件的使用协议中会声明“该软件的设计目的不是保障人身安全的,或用于与任何需要医疗设备的应用程序的连接,例如生命维持或车辆控制、安全设备或系统或任何其他可能导致死亡、人身伤害或严重的财产或环境破坏的应用程序。

EDA软件的上述声明主要是为了规避法律风险和排除责任。这些软件供应商担心在涉及生命安全的应用场景中,如果因设计错误导致设备失效,可能引发巨大的法律责任和诉讼风险。因此,他们在许可证和使用协议中明确规定其软件不得用于生命维持或安全设备的设计。

实际应用中,智能驾驶芯片的设计和生产流程中引入了多层次的验证机制,以确保其安全性和可靠性。芯片设计公司通常会通过多个验证步骤来补足EDA工具的潜在不足,包括:通过仿真和形式化验证来确保设计符合功能需求、将真实的硬件融入仿真环境进行大规模仿真测试和验证以及多重冗余设计以确保即使某个模块发生故障,系统仍然可以安全工作,具体设计包括驾驶环境监控冗余、MCU冗余、操控冗余(制动、转向)、通信冗余(控制信息传递)。EDA软件作为通用软件,不会考虑例如遵循诸如ISO 26262等功能安全标准,也要求芯片设计者和系统集成商承担起更多责任,并通过额外的措施来确保自动驾驶芯片的安全性和可靠性。

在芯片制造代工流程中,代工厂要求客户提交的设计文件通常有严格的格式和内容要求。这些文件提供芯片的详细设计信息,以便代工厂按照客户的设计进行制造。以下是代工厂可能要求的常见设计文件格式和内容:

1. GDSII(Graphic Data System II)文件

GDSII 是芯片设计最常见的标准文件格式,用于描述芯片的物理版图(layout)。它包含关于各层电路的几何形状和位置信息。GDSII文件的所有数据都是由一连串的数据块链接组成的。这些数据块大体上可分为文件头,模块结构头,图素头,图素,图素尾,模块结构尾,文件尾这几个部分,每个部分包含若干个模块,有些模块是必须包含的,另外一些则为可选的模块。每模块的前四个字节标志了该部分的元信息,第一二字节描述了该部分的size,第三四字节描述了该部分的type。GDSII包括布线、晶体管、接触孔等的几何形状和布局数据。代工厂利用 GDSII 文件来定义光罩(mask),从而用于后续的光刻和制造流程。

BGNLIB库文件头,它定义了GDSII文件最后一次修改的时间和读取时间,时间用6个int16数字来表示年月日时分秒。

2. SPICE 网表(SPICE Netlist)文件

SPICE(Simulation Program with Integrated Circuit Emphasis)网表 是描述芯片电路行为的格式,用于进行电路仿真和分析。网表列出芯片电路中所有元件的互连方式,包括电阻、电容、晶体管等元件的模型和连接关系。代工厂会根据 SPICE 网表来验证电路的功能和性能,确保芯片符合客户的电气规格。

3. 设计规则检查(DRC,Design Rule Check)报告

DRC 文件用于检查芯片版图设计是否符合代工厂的工艺设计规则。DRC通常由客户或第三方工具生成,包含关于版图是否符合代工厂提供的设计规则的验证结果。例如相邻叉脚距离应当大于代工厂要求的最小间距、每个金属层的金属密度符合要求、Latch-up效应等。代工厂使用 DRC 报告确认客户的设计可以在其工艺节点下可以成功制造,避免违反工艺限制。

4. 版图对电路(LVS,Layout Versus Schematic)报告

LVS 是一种验证报告,用于检查芯片版图与电路设计(原理图)的一致性。LVS包含对芯片的物理版图和电路网表进行比较的结果,以确保设计的布局与原理图中的电气连接一致,LVS可以确保元器件的各项参数链接关系与原理图保持一致。代工厂会要求 LVS 报告确认设计在物理布局层面和电路设计层面的一致性。

5. 参数提取(Parasitic Extraction)文件

Parasitic Extraction 文件用于提取设计中的寄生效应,如电阻、电容、感应等,这些效应会影响芯片的性能,同时列出芯片布局中寄生电阻、电容和其他不理想因素的模型和参数。该文件是代工厂利用这些数据进行后续的电路仿真,以确保芯片在实际环境中的性能符合预期。

6、功耗和时序报告(Power and Timing Analysis Report Report)

客户可能需要提交详细的功耗报告,特别是对于低功耗设计,说明芯片在不同工作状态下的功耗,同时描述芯片在各种场景下的功耗数据,如静态功耗、动态功耗、峰值功耗等。时序分析报告是一份描述芯片时序行为的报告,确保芯片设计在运行速度和时钟频率上符合要求。

这些设计文件的准确性和格式至关重要,因为它们直接影响芯片制造的成功与否。代工厂如台积电通常会有详细的设计提交要求,并提供工具和设计规则,以帮助客户生成符合工艺要求的设计文件。

在芯片的整个生产流程中,关于芯片制造的具体步骤和工艺的表述通常会非常详细,因为这是相关合同的重要组成部分之一。为了确保按照客户的要求生产芯片,相关制作流程中需要明确约定制造流程和工艺要求。以下是可能涉及的具体表述内容:

1. 工艺节点(Process Node)

明确芯片制造的工艺节点,例如5纳米、7纳米、14纳米等。工艺节点直接影响芯片的性能、功耗和密度,因此这部分通常是合同中的核心。

2. 晶圆材料(Wafer Material)

硅是最常见的晶圆材料,因为其丰富的资源和优越的电学特性。此外,砷化镓、碳化硅和其他化合物半导体材料也用于特定应用,如高频器件和光电器件。例如:“晶圆材料必须为12英寸硅晶圆,符合客户提供的材料规格书要求。”

在纯度方面,半导体用单晶硅片在9N(99.9999999%)-11N(99.999999999%)左右。在外观方面,半导体用硅片在表面的平整度,光滑度和洁净程度要比光伏用硅片的要求高。砂子到硅片需要经过轨锭熔炼、切片(Wafer Slicing)、抛光(Lapping&Polishing)等过程,最终形成一片片的晶圆(Wafer)。

代表性厂家:TCL中环,切片领域主要有高测股份,抛光领域主要有华特气体、鼎龙股份。

相关细节:晶圆的晶向密勒指数、机械抛光--无蜡贴片、化学抛光--可溶性硅酸盐的电荷吸附、热钝化流程中SiO?与栅氧电介质。晶片的清洗颗粒、金属杂质,利用液体介质和高纯氮气,以高压方式雾化后完成清洗。相关参数:喷雾角度、喷雾高度、喷雾粒径、喷射速度、冲击力损伤度。

3. 掩模版(Mask)和光刻技术(Lithography)的具体要求

掩模版(光罩)在芯片制作工程中需要几十套甚至更多(与曝光次数对应),客户可以通过第三方厂家定做或者直接委托给代工厂制作,掩膜版的制作费用根据制程可能需要数百万甚至上千万的成本。

光刻的基本原理为清洗--涂胶—软烘—曝光—显影—坚膜—显影检测(图像识别),其中正光刻胶是曝光区域溶解,而负光刻胶是未曝光区域溶解。

光刻的技术发展从最早的接触式光刻(1:1掩膜版)到重复光刻(掩膜版+调焦投影透镜)、步进光刻(不同的曝光光源)、沉浸光刻(折射率为1.44的超纯水)、EUV光刻(激光发射器-聚焦系统-掩膜版-投影系统)。

光刻胶配套试剂包括增粘剂,粘度与膜厚的相关度,在光刻胶之前预涂,涂胶嘴800r/min转速下旋转完成,还包括去边剂(高速旋转过程中高纯度、低颗粒,去除光刻胶),以及显影剂(溶解晶圆上不需要的光刻胶,例如四甲基氢氧化铵)。

4. 蚀刻与沉积(Etching and Deposition)参数

详细说明各层芯片材料的蚀刻和沉积工艺,包括化学气相沉积(CVD)、物理气相沉积(PVD)等方法。

蚀刻工艺随着芯片整体设计而变更,蚀刻工艺要求对蚀刻功率、压力、化学浓度、温度和时间的精准控制,蚀刻工艺商已经开始使用专用的建模软件以实现各个工艺参数的关联控制,同时对蚀刻过程的精准捕捉或者观测也十分重要,甚至是整个控制过程的关键,最后时间的精准控制是高效蚀刻的重要环节,任何细小的偏差都可能导致线条间距和通孔结构的变化,从而影响整体的稳定性。

从计算建模的角度,各个蚀刻参数的组合可能有无数种,但是最优方案的选取不仅取决于算法的设定还需要结合实际代工厂的反馈,才能在模拟环境中确定最后的组合方案。

5. 离子注入(Ion Implantation)

描述半导体器件中使用的离子注入工艺,规定离子注入的类型、能量和深度等。

通过分离和加速,将离子束注入到固体材料表层以改变物理性质,以调整导电性为主。以硼离子、磷离子为主。应用场景:深埋层、倒掺杂阱、阙值电压调节、形成PN结。细节包括离子源(正离子)、分析磁体、加速管(串联电极)、扫描盘、静电中和系统、真空腔。

6. CMP(化学机械抛光,Chemical Mechanical Planarization)

抛光程序是指晶圆表面平整化的步骤,确保每一层材料在沉积和蚀刻后能够保持平整度。一般在湿法刻蚀、浅槽隔离后、金属沉积后等多个程序均需要抛光程序,其中抛光液浓度、打磨片致密度和转速、颗粒大小(纳米级)、成分和浓度等数据都是重要的工艺参数,对抛光工艺过程中的温度、度量控制也都是工艺厂的重要商业秘密。

CMP程序中对质量、大小、尺度的检测和度量也是重要的技术基础,例如无接触测量表面和材料(包括反射表面)的距离和厚度的技术,以单个控制器、单个高精度传感器头、2 至 10 kHz 的最大测量频率实现亚微米精度测量技术。

7. 金属互连与封装(Metallization and Packaging)

明确金属互连工艺(如铜或铝互连)以及芯片封装技术(如倒装芯片封装、CSP、BGA等),包括金属材料的选择和互连层的数量。“未来芯片发展,不再看制程,而应该看封装”。安靠(Amkor)、日月光(ASE)、长电科技、ASM Pacific、K&S、Besi、Towa、Yamada等公司占据了绝大部分的封装设备市场,大陆可以完成传统封装的工厂已经有将近两百家。

封装的发展:晶体管封装、双列直插封装、引出线封装、引脚阵列封装(有线封装,触角数量有限)、2.5D立体封装(CoWos)、3D堆叠封装(Wafer on Wafer)。现代封装引脚线超出2000个,传统的引脚封装不能满足。

芯片级晶粒尺寸封装(WLCSP Wafer Level Chip Size Package),台积电称InFO(Intergrated Fan-Out), 程序上在提早到切割前封装。日月光也掌握这个技术。CoWos(Chip on Wafer on substrate),利用10微米的硅中介板(interposer)将晶片水平排列(不能上下叠)封装在一起。

3D堆叠封装最早的构想来自1965年诺贝尔物理奖获得者Richard Feynman在1985年的演讲,他共享了芯片的多层集成构想。后来日本政府在1990年资助了相关的3D研究,但是限于硅表面清洁度、平整度和洁净室级别等客观原因,长期处于基础研究状态。

3D可以上下重贴放置,在芯片内制作硅穿孔(TSV),量产时可以堆叠8层芯片,但是目前多用于DDR(高频存储芯片)。处理器暂时只能以CoWos封装。3D封装相对于传统封装的要求更高,挑战更高,裸晶的平整度要求更高,要求晶片对准度(堆叠时节点需要对齐)会影响良率,密度高导致热传导效应增加,温度高会影响散热,影响效能,严重的话会使产品失效,所以会自动关机。高熱导系数的材料研发需求,砷化镓,磷化铟,碳化硅(功率元件),氮化镓(原子排列工整),氧化镓(临界电场高),钻石(C)。

芯片背面通过热界面材料(TIM)粘附到散热片上,来自髙功耗的芯片大部分热量可以通过散热片散失,低功耗的MEMS/CMOS传感器采用倒装芯片或引线键合形式。实验数据显示,顶部带有4个散热片芯片的转接板可以将平均芯片温度105℃降到57℃。

芯片温度不均匀造成的热梯度不可避免。在精心设计的整体产品架构中,可测试性设计 (DFT) 这一重要考量因素须涵盖产品的所有功能部分。热管理基于芯片的电子设备是最大的之一提高性能和集成密度的瓶颈。虽然每次操作的能量在增加,但越来越多相同面积的晶体管越多,密度就越大耗散功率达到不可接受的水平,威胁到当前行业的发展速度。

8. 良率控制与质量保证(Yield Control and Quality Assurance)

芯片代工合同一般都会明确良率(Yield)的目标要求,并规定如何处理不合格产品。合同中可能包括对良率的监控和改进措施。代工厂在制造过程中及成品后的电气测试和性能验证,通常包括功能测试、热测试和老化测试等。

9. 芯片测试(Testing)

描述在芯片进行的测试和筛选程序,确保最终产品符合客户的性能标准。测试按照测试方法又可分为测试机(ATE)、分选机、探针台,按照工序可以分为晶圆加工环节测试以及封装后的成品测试。在半导体测试设备(ATE)领域,美国泰瑞达(Teradyne)、日本爱德万(Advantest)、美国科休(Cohu)占据了数字及SoC类芯片、存储类芯片等领域主要市场份额。SoC的关键构成是IP核,当核被集成到系统内部后,很难通过系统的输入对内部核施加有效的测试数据,并从系统的输出捕获内部核的响应,因此SoC测试机难度非常高,需要持续研发以适应高端芯片的技术标准和协议

国内的ATE厂商包括华峰测控、长川科技、亚威股份、华兴源创、联动科技等。封装测试技术,已经由最初的封装后向电路设计环节进行延长,同时AI测试软件也开始占领一定的市场份额。

用于汽车行业的芯片往往适用更高层级的测试标准,ISO26262把安全等级做了划分,常见的有ASIL-B和ASIL-D级。ASIL-B要求芯片能够覆盖90%的单点失效场景,而ASIL-D则是99%。这其实是个非常高的要求。一个晶体管的失效概率虽低,可是通常一个复杂芯片是上亿个晶体管组成的,如果不采取任何措施,那任何一点的错误都可能造成功能失效,失效率很高,

在芯片制造和测试过程中,自动化测试设备(ATE)和探针台是关键的测试工具,主要用于确保芯片在不同阶段的功能、性能和可靠性达标。这些设备在芯片从晶圆阶段到成品芯片的各个环节中都起着重要作用。

ATE的基本作用是(ATE)用于对芯片进行批量的功能和性能测试,确保每个芯片都满足设计要求。它通常用于晶圆测试(也称为“裸片测试”)和封装后测试。ATE设备高度自动化,能够在较短的时间内测试大量芯片,广泛用于生产线上的大规模生产测试中。

ATE的组成

测试控制器:控制ATE的核心部件,用来运行测试程序并发送测试指令。它通过接口与被测芯片(DUT,Device Under Test)进行数据交互。

信号发生器:用于生成特定的电信号并输入到被测芯片,以模拟芯片工作时的实际环境。例如,信号发生器可能产生不同的电压、频率和波形,以模拟芯片在不同工作条件下的表现。

数据采集模块:用于采集和分析芯片输出的信号。通过对比芯片输出的信号与预期值,判断芯片是否满足设计要求。

测试夹具和接口板:测试夹具用于将芯片与ATE设备进行物理连接,而接口板则充当芯片与ATE控制器之间的桥梁,确保信号能够正确传输。

自动化装置:自动化设备如机械手等用于在测试过程中自动将芯片放入或取出测试座,提高测试的效率。

ATE的测试类型

功能测试:验证芯片的各项基本功能是否正常工作。例如,测试处理器的指令执行是否准确,存储器的读写是否正确。

时序测试:ATE通过对芯片的信号传输时间进行测量,确保芯片在规定时间内完成信号处理。时序测试至关重要,因为稍微的延迟可能会导致芯片功能失效。

电源测试:验证芯片在不同电源条件下的工作情况,包括电源完整性、电压波动和功耗等。

环境测试:一些ATE系统还可以模拟不同的环境条件(如温度和湿度),以评估芯片在恶劣条件下的表现。此类测试确保芯片能够在广泛的环境下正常运行。

ATE的应用场景

晶圆测试:在芯片封装前,将裸片进行测试。ATE与探针台结合使用,通过探针直接接触晶圆上的芯片进行测试。这种测试有助于识别在制造过程中出现的问题,并决定哪些裸片可以继续进行封装。

封装后测试:在芯片封装之后,ATE再次对芯片进行全面的测试。这时,ATE将检查芯片的整体功能,包括引脚的连接、电气性能、稳定性等。

法律角度的关注点

* 测试设备采购合同:律师在帮助企业采购ATE设备时,需特别关注设备性能、保修条款、软件升级和技术支持的约定。

* 知识产权与设备授权:部分ATE设备中使用的软件可能涉及专有技术或软件许可,律师需确保使用协议中对知识产权的归属和使用范围有明确规定。

* 责任划分与测试准确性:如果由于测试设备故障导致芯片未能通过测试或测试结果不准确,可能引发责任纠纷,律师需协助企业厘清各方的责任范围,特别是在使用第三方测试服务时。

据美联社报道的历史数据,三星半导体和LCD工厂的200多名员工染上重病,其中至少76人死亡。自2008年以来,56人已向政府提出获得职业安全赔偿。韩国工人安全组织Banolim公布的文件显示:近年来,该组织已经收录有200余例严重病例在案,患者均为前三星半导体和液晶生产工厂员工,他们在韩国三星工厂接触了有毒化学物质后,出现了白血病、狼疮、淋巴瘤和身体组织多处硬化等不同的病症。目前已经造成76人死亡,员工年龄均在20至30岁。

2024年5月30日消息,韩国核安全部门对三星电子展开了一项重要调查,调查起因是该公司在其一家芯片工厂内发生了一起辐射暴露事件,涉及两名工人。

1. 化学品

光刻胶(Photoresists)包含溶剂、树脂和光敏化学物质(酚醛树脂、聚异戊二烯),配方和配比都是高度保密的,可能释放挥发性有机化合物(VOCs)并引发头痛、呼吸道刺激,长期接触可能导致慢性健康问题。

光刻去除剂(Strippers)使用酸性或碱性化学物质,如四甲基氢氧化铵(TMAH),对皮肤和眼睛有腐蚀性,吸入可能危害呼吸道。

蚀刻过程中的化学气体如六氟化硫 SF? 和四氟化碳 CF?,他们用于等离子蚀刻,具有高毒性,可能导致窒息,长期暴露有损肺部健康。

硫酸、磷酸、氢氟酸,用于湿法蚀刻以清洁和修饰芯片表面,以上酸是剧毒物质,可通过皮肤吸收导致严重中毒或死亡。

化学机械抛光(CMP)化学品如纳米颗粒悬浮液,主要成分包含氧化铝、二氧化硅等化学物质,用于抛光芯片表面。

2. 放射源,主要为X射线,用于芯片制造中的无损检测(Nondestructive Testing,NDT)和缺陷分析,过量暴露可能导致放射性疾病,包括皮肤灼伤和癌症。 放射源也包括离子注入时高能加速的离子(如磷、砷、硼),用于注入硅晶片,改变其电学性质。涉及高能辐射,可能危害操作者健康。

3、重金属如砷(Arsenic)和铍(Beryllium),主要用于离子注入工艺,作为掺杂剂。重金属可导致神经损伤和癌症风险。应当限制暴露水平,处理含砷废料时使用专门设备。

4、职业风险控制

配备高效的通风系统和过滤装置,防止有害物质扩散。设置专门的废水、废气处理设备。个人防护包括佩戴化学防护手套、防毒面具、防护服和定期健康监测。

如果合同违约或商标/专利侵权很容易被发现和处罚,那么竞争对手非法获取竞争对手的技术机密的其他替代方法可能更难追踪。从理论上来讲,芯片的金属层、隔离层、链接器件、封装层可以通过逐层打磨(对精细度要求较高)展现,对于化学涂层可能还需要特定的化学溶液(需要推测对方使用的化学沉积工艺),可能还是使用到高能离子束用于精准的切割,同时利用扫描电子显微镜(SEM)、能量色散X射线光谱仪等逆向设备进行分析,通过这些逆向方法并结合一些版图提取软件(NetEditorLite)可以获得竞争厂家的晶体管尺寸、引脚间距、隔层材料等数据,但是芯片制造的详细工艺是很难获取的,而且这些固件的信息也很难反馈固件的开发工具数据和相应的代码。后续的电路仿真也需要逆向工程师具有专业的技术背景,结合竞争厂家的芯片数据手册,逐一将电路、寄存器、联接方式进行提取和整理。整体来讲,时间和成本都是非常高的。对于高制程的芯片来讲,从制作流程以及芯片生态来讲,搞一个“山寨芯片”的商业性是值得怀疑的。

用于芯片失效分析的芯片开封技术(Decap)在某种程度上与上述逆向拆解类似,但是两者的目的是完全不同的,失效分析是针对自家开发的芯片,而逆向拆解则是针对竞争对手的。

同EDA软件一样,不同的厂家都会针对竞争对手可能采取的逆向工程采取特殊的防破解工艺,在版图的设计图保护过程中,逆向分析是维权诉讼中重要的环节,否则很难将取得初步的证据。

芯片产品的逆向拆卸可以初步获取芯片产品的封装、内部电路板和元件,也有公司使用这些数据来提供物料清单和制造的暂定成本。逆向分析师可以在需要的地方(某一层打磨之后)安装探针(有时非常困难,但通常可以做到)。探针可用于监控芯片上的信号,前提是必须开发测试用例,并创建信号源以使芯片在功能模式下运行。通过信号发生器、逻辑分析仪和示波器用于驱动系统并收集结果,然后分析信号和整个系统。

芯片的电路提取随着每一代产品的出现而变得越来越困难,芯片在设计时也越来越多的考虑防止逆向的分析,包括加密代码和物理防拆解的设计,这些防逆向的设计从最初的设计环节一直到封装环节,都是高度保密的。

当然,有经验的逆向分析人员在知道处理器和指令集,就可以使用特定的逆向程序帮助获取汇编代码并将其构造为更像 C 的格式。然后软件专家可以分析这种结构化代码。为了对抗这些威胁,混淆已成为半导体或硬件 IP 保护的重要手段。混淆技术旨在隐藏或锁定半导体产品的底层知识产权,例如 IP 核、门级设计或布局,以防止不受信任的一方或对手进行逆向分析。各个设计厂商都在研究新的 IP/IC 混淆方法,包括芯片编辑兼容网表和布局修改以保护小批量产品的 IP、使用更高的加密标准在设计流程中以保护 IP 机密性和完整性。

芯片逆向的市场需求也催生了以无损断层扫描的设备和技术,例如射线断层扫描是一种用于无损三维 (3D) 成像的先进技术,利用最先进的分析软件对部分多层芯片的逆向工程分别可以在数小时内以半自动化方式完成。但是,扫描结果并不意味着逆向分析可以“喝咖啡式悠闲”的方式就可以完成芯片的逆向工程,因为芯片的镀层内部会添加特殊防逆向材料以阻挡类似的射线扫描,从而导致断层扫描结果产生噪音和伪影。

防止逆向工程的时间和成本会汇入芯片的最终成本,从单纯的使用者角度,这样的成本支出是完全的“浪费”,对芯片的设计保护也需要完善的法律保护环境支持。

探针台是芯片制造过程中用于晶圆测试的关键设备。它允许对尚未封装的晶圆上的裸片进行测试,是ATE在晶圆测试阶段的重要配合工具。探针台通过微小的探针接触晶圆表面上的芯片引脚,将信号传输给ATE,以进行电气测试。

探针台的组成

微调工作台:探针台上的工作台能够进行极其精确的调整,使得探针能够对准晶圆上的特定位置。精确度极为重要,因为现代芯片的引脚非常小,容差极小。

探针卡:探针卡上安装了多个微小的探针,用于接触芯片的电气连接点。探针卡通常是根据特定晶圆设计定制的,以匹配芯片的引脚位置。

光学系统:用于帮助操作者准确定位探针和晶圆。随着自动化程度的提高,许多探针台配备了自动对准系统,利用图像识别技术进行精确定位。

温控系统:有些探针台配有温控系统,以测试芯片在不同温度条件下的电气性能。这对于汽车、航天和其他对温度敏感的行业应用尤为重要。

探针台的测试流程

晶圆加载:将晶圆放置在探针台的工作台上。自动化的探针台能够一次性加载多个晶圆,提高测试效率。

探针对位:操作者或自动化系统根据晶圆设计图定位探针,使其精确接触芯片的电气引脚。探针对位的精确度决定了测试的有效性。

测试执行:探针与ATE设备连接后,ATE向晶圆上的芯片发送测试信号,并根据反馈分析芯片的性能。

数据采集与分析:测试结果通过探针卡反馈给ATE,ATE分析芯片的电气性能并记录测试数据。如果芯片未通过测试,则标记为“坏片”,在后续封装时会被剔除。

探针台的应用场景

探针台主要用于对裸片进行测试,在芯片封装前确认芯片是否满足设计要求。通过早期测试,可以避免将有缺陷的芯片进行封装,从而减少生产成本。同时,在芯片开发和验证阶段,探针台用于反复测试和调试设计,帮助设计人员验证芯片的功能。

法律角度的关注点

类似于ATE设备的采购,探针台的性能、维护和升级条款需明确规定。由于探针台的精密度要求极高,法律合同中还应包括故障处理和技术支持的具体细节。

探针卡的定制化和精度要求很高,如果由于探针台设备的问题导致晶圆损坏或测试结果失准,律师需帮助企业明确供应商和设备使用方的责任划分。

在芯片制造过程中,封装技术是将芯片从制造完成的晶圆形态转换为可用的独立组件的关键步骤。虽然封装技术的基本原理是公开的,但在实际实施过程中,许多细节、工艺流程和技术诀窍涉及公司核心竞争力,因此被视为商业秘密,而不是通过专利进行保护。芯片公司通过商业秘密的形式保护这些技术信息,避免在公开专利时可能面临的知识泄露风险。

1. 商业秘密保护在芯片封装中的重要性

封装技术不仅仅是将芯片进行物理保护和电气连接的过程,还会极大地影响芯片的性能、功耗、散热、尺寸和可靠性等方面。例如,先进的封装技术可以提升芯片的散热能力,延长其寿命,甚至决定其在不同应用领域中的适应性。因此,尽管封装工艺的基础原理是公开的,但实际实施中的工艺优化和特定方法往往成为公司之间竞争的重要因素。

芯片公司在封装过程中积累了大量关于如何提升封装效率、提高芯片可靠性、降低成本等方面的技术诀窍,这些信息一般不通过专利公开,而是作为商业秘密进行保护。这些秘密往往包括具体的材料配方、工艺参数、制造流程和质量控制方法等,属于公司的无形资产和技术壁垒。

2. 封装技术中常见的商业秘密类型

封装材料:不同封装技术中使用的材料种类(如粘接剂、封装基板材料等)及其配比可能是公司的独家配方,能够影响芯片的散热性和耐久性。

封装工艺参数:精确的温度、压力、湿度等工艺参数的调节是影响封装质量的关键。这些参数经过反复调试,得出的最佳值往往成为技术诀窍,不便公开。

封装工艺流程顺序:不同的工艺流程安排可能显著影响生产效率和成品率。某些公司通过优化生产线的布局和操作顺序,能够有效降低成本并提高产品质量,这些细节通常是商业秘密。

封装设计与结构细节例如芯片的封装设计结构包括引线框架、倒装芯片封装(Flip-Chip)、扇出型封装(Fan-Out)、系统级封装(SiP)等封装方式。这些封装结构的设计如何与特定芯片进行匹配,如何最大化其电气性能和机械性能,也是企业的技术核心:

热管理设计:封装中的散热方案设计,包括导热材料、散热通道设计和封装几何结构的优化,这些设计可以显著提高芯片的热管理能力,但相关细节不会公开。

电气设计:封装中的电气连接设计、如何最小化信号传输中的延迟和噪声、以及如何提高电气性能,这些设计通常涉及复杂的模拟电气特性计算和实验验证,属于高度保密的内容。

封装设备与工具的定制化调整:芯片封装中的设备和工具使用也可能经过定制化调整以适应特定工艺流程。例如,某些封装设备的硬件或软件部分可能专门为一家公司定制,能够优化生产效率、减少次品率或提高质量控制。设备使用中的调整经验和配置也属于商业秘密范畴。

质量控制与检测标准:在封装过程中,如何制定和实施质量控制标准也是商业秘密的重要部分。不同公司可能开发出独特的质量检测方法或标准,用于检测封装的完整性、密封性、引脚连接质量等。这些标准和检测手段往往能够确保芯片的高可靠性和性能,是公司的一大竞争优势。

供应链与成本管理策略:封装材料的供应链管理和成本控制策略也是商业秘密的重要组成部分。公司可能通过与特定供应商建立长期合作关系,以获得成本优势,或通过特定采购策略降低封装材料的成本。封装材料的替代方案、供应链管理策略等,都会直接影响公司的盈利能力和市场竞争力。

为了有效保护封装技术中的商业秘密,企业必须采取一系列法律、技术和管理措施,防止信息泄露:

信息隔离:在封装工艺的设计、优化和实施过程中,公司可以采用信息隔离的方式,确保每个参与者只能获取与其工作相关的部分信息,而不会了解整个工艺流程。这可以防止单个员工掌握过多核心技术信息,从而降低泄密风险。

分级访问权限:对不同级别的员工和合作伙伴,给予不同的访问权限。只有经过授权的人员才能访问封装工艺中的关键参数和敏感数据。

监控与审计:公司应对核心工艺的数据访问和操作进行监控,记录操作日志,定期审计,以确保敏感信息不会被未经授权的人员访问。

员工培训:公司应定期为员工进行商业秘密保护培训,使其充分了解保密义务以及违反保密义务的法律后果。员工需要知道哪些信息属于商业秘密,如何正确处理敏感信息,以及在遇到泄密风险时如何报告。

离职管理:在关键技术人员离职时,公司应进行全面的离职面谈,提醒其遵守保密和竞业禁止协议,并确保其没有携带任何公司机密材料离开。

从公司的角度,芯片行业的技术秘密关乎产品良率与企业核心竞争力,一旦竞争对手通过招揽离职员工的方式获取了商业秘密,则资本巨额的前期投资将化为乌有,其后果也是非常严重的。

我们在《高管离职筹划》的文章里曾就如何区分行业经验和商业秘密进行过讨论,也曾向高科技公司的高管提供过一对一的法律咨询,我们认为,应从以下角度划分两者的界限:

1、我们认为行业经验是技术人员多年积累的专业知识、解决问题的能力和通用技能,这些属于个人能力,应该受到尊重和保护。而商业秘密通常是指公司内部未公开的芯片技术数据、芯片制造工艺、产品设计等特定信息。在跳槽前,技术人员应仔细区分哪些知识和信息是自己的工作经验,哪些是公司明确保护的商业秘密。技术人员在离职前应仔细阅读公司的保密协议,明确哪些内容是保密义务的范围,避免误用这些信息。

因为技术人员对法律实践缺乏必要的了解,建议咨询专业律师,确保对自己责任和权利的清晰理解。

2. 避免带走公司机密文件或材料

无论是纸质文件、电子数据还是笔记,技术人员离职时都应完全归还,并且不能在新公司中引用或使用,即便某些内容在工作中是自己整理或创建的。同时,技术人员离职时可与公司进行清楚的交接,以表明自己没有带走任何保密材料。

3. 强调行业知识的合法使用

行业经验和通用技能是技术人员多年积累的成果,可以在新岗位上合理、合法地加以利用。例如,对于一般的技术知识、技能操作或问题解决能力等,不涉及特定的原公司秘密或专有信息,可以合法使用。如果担心法律风险过高,技术人员在竞业禁止协议的范围内考虑从事不与原公司直接竞争的岗位或项目,以有效降低侵犯商业秘密的风险。

4. 商业秘密保护手段的边界

一些大型的芯片公司会部署内部安全监控系统,对员工的系统访问行为进行实时监控和日志记录分析,发现异常行为时立即采取措施。近期部分公司还在利用大数据分析和人工智能(AI)技术,对员工的行为数据进行监控和分析,以识别异常行为模式,这些模式可能指向潜在的违规活动。

但是技术手段的过度使用,忽略了技术人员作为“人”的感知而不是机器行为,过度的技术手段会减弱员工对公司的认同感和归属感。

在某公司前芯片设计师被起诉的案件中,设计师在职期间与新设公司合伙人的通话时长被作为后期起诉的证据,前公司认为其在职期间的通话时长超出了必要的商务沟通范围,并且前公司的员工也出庭作证,声称设计师在招揽过程中表明新公司的筹划处于“stealth”状态,前公司还拿到了该名设计师与其他拟招揽员工的短信内容,尽管个人通讯的内容是否是个人隐私的讨论在上述案件中仍然可能有争议,但是就保护的边界仍需要结合对“人性”的理解和尊重为前提。

5、高科技企业对员工监管与商业秘密保护的关系

中国文化里讲“留俗庸陋之规日甚,而人之日趋污下”,说的就是环境、规则与人之间的互动关系。

采用 2nm 和 3nm 工艺节点制造的尖端半导体每片晶圆可卖到约3万美元,而传统芯片节点每片晶圆仅卖到几百美元,其中数额差异,高科技公司保护商业秘密的需要是显而易见的,尤其是在竞争激烈的芯片行业中,技术和信息的泄露可能会对公司的生存构成威胁。然而,过度监控员工、将其视为“机器”进行管理,可能会损害员工的自主性和创造力,甚至导致信任缺失,从而影响公司的文化和员工的归属感。

对员工的监管要根据职位、责任和敏感度的不同来区别对待。对于研发人员和技术核心员工的监管可能需要更严格,但对于其他岗位的员工,则可以适当放松,以避免过度监管带来的不适感。同时,使用AI和大数据技术进行智能监控,以减少人工监管的侵犯感。通过自动化和智能化手段,可以实现对敏感信息的保护,而不需要时时刻刻监控员工的行为。

在高度强势的企业文化中,员工通常会更倾向于遵循公司制度和领导的指示,而不会过于关注个人隐私的侵犯。中国的法律环境也在逐渐适应现代化,虽然隐私保护的法律体系已在建设中,但相对于西方国家,隐私保护意识和法律执行尚未形成非常成熟的体系。因此,在中国企业中,特别是部分领导管理风格十分强势的企业中,员工对监控的容忍度可能会相对较高,员工可能更理解公司出于保密需要实施监控的做法。而且在中国文化中,对员工的监管措施更多被赋予一种“保护性”的标签(例如,保护公司核心技术、避免竞争对手盗用员工的创意),可能会更容易被理解和接受。

但是,这并不意味着员工对过度监管毫无底线的认可,尤其是在公司监管措施缺乏透明度或者已经发生纠纷时。因此,虽然文化上更容忍监管,但管理者仍然需要通过建立信任关系,减少“高压管理”的印象。

6、减少对工作经验与公司商业秘密边界的误解

关于工作经验与公司商业秘密的界限问题,确实没有一个绝对、统一的标准。每位技术人员的成长经历、技术积累方式、在公司的具体岗位、参与的项目类型等各不相同,这些因素会在个案中呈现出独特的情况。此外,技术人员的个人性格、价值观、对职业发展的预期等主观因素,也会影响他们对“工作经验”与“商业秘密”界限的理解和接受程度。因此,不同的技术人员在离职时,可能会对自身掌握的信息和技能是否涉及公司秘密产生不同的看法和行为选择。

由于这些客观与主观因素叠加,形成了该问题的复杂性和高度个性化特征。法律在保护商业秘密与尊重个人工作经验的界限方面虽有原则性规定,但在实际操作中,个案之间存在很大的差异。因此,对于技术人员来说,在面临离职或转岗时,理解自身权利与义务的边界,避免法律风险显得尤为重要。

在这种情况下,建议技术人员根据自身情况,结合公司保密协议的具体条款以及个人职业发展计划,与专业律师进行一对一咨询。这种个案咨询可以帮助技术人员深入理解在自己特定环境中的风险和法律义务,并获得专业的建议,以在离职或职业转换中有效地保护个人权益,避免不必要的法律纠纷。

在芯片设计或制造领域,高级员工离职后因泄露商业秘密而被追究责任的案例相对较多。这些案例通常涉及技术高管或核心研发人员。以下是一些典型的案例:

1. TSMC与三星的商业秘密案

台积电(TSMC)是全球领先的半导体制造公司,而三星是其主要竞争对手之一。在2015年,几名原TSMC的高级工程师被指控在离职后跳槽至三星,涉嫌将TSMC的制程技术带到三星。台湾的检方起诉这些工程师,指控他们窃取商业秘密,并试图将这些秘密带到竞争对手公司。该案件引发了关于如何保护半导体行业商业秘密的广泛讨论。

2. 英特尔(Intel)与AMD的商业秘密案

2008年,英特尔起诉其前高管Fran?ois Piedno?l,指控他在离职后加入竞争对手AMD时,非法带走了数百份敏感文件,其中包括了英特尔的处理器设计文件。

英特尔指控Piedno?l违反了其竞业禁止协议,并要求对其进行法律追责。最终,该案件通过庭外和解方式解决,但这次事件突显了芯片行业内商业秘密保护的重要性。

3. 中芯国际(SMIC)与台积电的商业秘密案

2003年,台积电指控中芯国际(SMIC)窃取其先进的制程技术,并将其用于自身的芯片生产。这起案件涉及多名离职的台积电员工,他们在加入中芯国际后,被认为将原公司的技术秘密带到了新公司。台积电在美国加利福尼亚州起诉中芯国际,并最终获得了有利的判决。中芯国际同意支付和解费用并达成协议,以避免进一步的法律追诉。

4. ASML与XTAL的商业秘密案

ASML是全球领先的光刻设备制造商。2019年,ASML起诉前雇员及其创办的公司XTAL,指控他们窃取ASML的商业秘密。除了 8.45 亿美元的判决外,审判法院还发布了一项禁令。该禁令要求 XTAL 不得对 ASML 声称受到其知识产权污染的软件产品进行任何软件开发活动,并明确允许 ASML 联系 XTAL 的实际或潜在客户,并告知他们陪审团的裁决和诉讼结果,并禁止 XTAL 在一定时期内继续从事与 Brion 相同的业务领域。两名离职员工对指控表示认罪(其中一人将 ASML 的 OPC 软件源代码全部 200 万行下载到硬盘上),最终一名被判处七个月电子监控,另一名被判处 90 天社区服务。

与此同时,尽管 XTAL 造成了混乱,ASML 也一直在努力确保最初被 XTAL 挖走或试图挖走的 ASML Brion 客户能够继续获得 ASML 的计算光刻产品支持。陪审团于 2018 年 11 月作出裁决,而最终判决于 2019 年 5 月 3 日作出,这期间出现延迟的原因是 XTAL 试图在初审法院作出最终判决之前申请破产,以避免这一结果。在破产案中,XTAL 试图出售其知识产权,而 ASML 在审判中证明其知识产权受到了ASML 商业机密的污染。破产法院批准了 ASML的动议,并将案件发回初审法院,以便法院作出最终判决,目前法院已经作出最终判决。

破产法院批准的和解安排提供了确定性,并结束了双方之间的所有诉讼,包括初审法院、上诉法院、破产法院和仲裁,此外,ASML 还获得了 XTAL 的大部分知识产权。

5、YU与马萨诸塞州ADI芯片商业秘密案件

2014 年至 2017 年期间,YU(出生于哈尔滨后入籍美国)在 ADI 公司工作,负责设计通信、国防和航空航天行业使用的微芯片。在工作期间,余接触到了 ADI 公司的各种知识产权,包括现有和未来的微芯片设计、原理图、布局、建模文件、客户名单和订购历史记录。

在 ADI 公司工作期间,余利用这些信息创办了自己的微芯片公司 Tricon MMIC, LLC。后来的取证分析显示,余的个人家用电脑中保存着数百份 ADI 知识产权文件的副本。庭审证据表明,余曾在 ADI 的安全服务器上访问过这些文件,复制了这些文件,更改了文件名(通常是卡通人物的文件名),然后将其保存在他的个人电子账户和设备上。

庭审证据显示,余某公司出售的所有芯片均采用窃取的 ADI 知识产权制造。具体而言,余某利用窃取的 HMC1022A 设计制造了两款 ADI 芯片的仿制品。随后,在 ADI 向市场推出其完整的设计之前,余某就开始向 ADI 的客户和其他公司出售其仿制品 HMC1022A。在余某被捕之前,他总共制造了约 10,000 块采用窃取的 ADI 知识产权制造的芯片,获利约 235,000 美元。2022 年 4 月,联邦陪审团宣判YU对起诉书中指控的 18 项指控不成立,但他被判犯有一项持有被盗商业机密的罪名。

尽管我们仍然可以看到高通(Qualcomm)与 苹果(Apple)、英伟达和三星、GlobalFoundries vs. TSMC的专利侵权诉讼,除标准必要专利(SEPs)(该部分详见后文介绍)涉及的通讯技术、接口协议、加密和安全协议属于例外的情形,------以下部分内容删减。

部分内容删减。

典型的 SEPs 纠纷案例

1、高通 vs. 苹果

背景:苹果认为高通收取的 SEPs 许可费过高,且不符合 FRAND 原则。

结果:双方在全球范围内展开专利诉讼,高通胜诉后,苹果最终支付和解金。

2、InterDigital vs. 华为

背景:InterDigital 是一家专注于无线通信专利的公司,曾多次起诉华为侵犯其 SEPs。

结果:案件通常以和解或交叉许可的方式解决。

------以下部分内容删减。

芯片投资律师审查建议

------以下部分内容删减。

部分内容有删减,欲了解全部内容,请联系作者 。