骨动力钻头都有哪些PCB板制造全流程工艺解析与实战指南

本文还有配套的精品资源,点击获取

简介:PCB(印刷电路板)是电子设备中的核心组件,其制造过程涉及设计、光绘、蚀刻、钻孔、镀铜、表面处理及测试等多个精密步骤。每个环节都直接影响产品的性能与可靠性。本文系统介绍了PCB板的完整工艺流程,涵盖从电路设计到最终切割封装的关键技术要点,强调质量控制与环保要求,帮助读者全面掌握PCB生产的核心原理与实际操作规范。

印制电路板(PCB)由导电层(铜箔)、介电层(如FR-4)、过孔、焊盘及阻焊层等组成,其核心功能是实现电气连接与机械支撑。多层板通过压合工艺将多个信号层、电源层和地层集成,典型结构包括四层板(Top Layer - Signal1, Inner Layer1 - Power, Inner Layer2 - GND, Bottom Layer - Signal2),各层间通过盲孔、埋孔或通孔互连。合理分层可提升信号完整性(SI)与电源完整性(PI),降低电磁干扰(EMI)。例如,地平面作为信号回流路径,应保持完整并靠近高速信号层,以减小环路面积极限噪声辐射。

| 层类型 | 功能说明 | 设计建议 |

|---------------|------------------------------------|------------------------------|

| 信号层 | 传输数字/模拟信号 | 避免跨分割,控制走线长度 |

| 电源层 | 提供稳定电压 | 使用整片铜皮,避开热源 |

| 地层 | 信号回流与屏蔽 | 连续无割裂,低阻抗连接 |

| 阻焊层(Solder Mask) | 控制焊锡覆盖区域 | 开窗精准,防止桥接 |

| 丝印层(Silkscreen) | 标识元件位号与极性 | 避开焊盘,提高可读性 |

高速信号在传输过程中易受反射、串扰和延迟影响,关键在于控制特性阻抗(Z₀)。常见单端50Ω、差分100Ω需通过叠层工具(如Altium Layer Stack Manager)设定介质厚度(H)、线宽(W)和介电常数(εᵣ)来计算:

Z_0 approx frac{87}{sqrt{varepsilon_r + 1.41}} lnleft(frac{5.98H}{0.8W + T}

ight)

其中T为铜厚。使用EDA工具进行约束驱动布线(Constraint-Driven Routing),设置差分对等长(±5mil)、走线间距≥3W以抑制近端串扰,并启用长度调谐(Interactive Length Tuning)确保时序匹配。

在Altium Designer中完成从原理图到PCB的闭环设计:首先创建原理图符号与PCB封装,关联Footprint至器件;通过“Design → Update PCB”导入网络表;设置电气规则(Electrical Rules)与布线规则(Routing Widths, Clearance);利用“Differential Pairs”定义USB或PCIe差分信号;执行扇出(Fanout)后自动布线结合手动优化,最后运行DRC检查短路、未连接等问题。

// 示例:Altium中设置差分对规则

Rule Name: USB_D+/_-

Type: Differential Pairs Routing

Pair: USB_D+, USB_D-

Target Nets: USB_D+, USB_D-

Routed Length: 80mm ± 0.2mm

Gap: 6mil (Edge-to-Edge)

Eagle与Cadence SPB同样支持层次化设计与高速约束管理,后者在复杂背板设计中具备更强的仿真接口能力。通过典型射频电路案例,在Layout阶段实施地平面分割隔离模拟/数字域,并添加非功能性焊盘(Non-functional Pad)减少寄生耦合,显著提升系统信噪比。

graph TD

A[原理图绘制] --> B[封装库匹配]

B --> C[网络表导入PCB]

C --> D[叠层与规则设置]

D --> E[布局:按功能模块分区]

E --> F[布线:优先关键信号]

F --> G[DRC+电气规则检查]

G --> H[生成Gerber与钻孔文件]

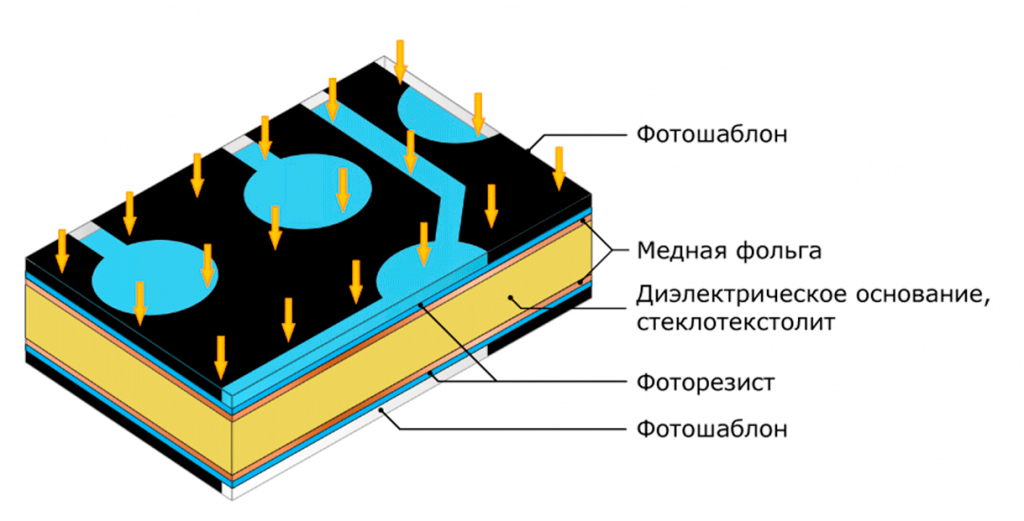

在高密度、高性能PCB制造流程中,光绘与光刻是决定图形转移精度的核心环节。从设计数据到物理线路的转化过程中,光绘负责将数字信息编码为可被曝光设备识别的格式,而光刻则通过精密的光学系统将这些图形准确复制到涂覆有光刻胶的基板上。该过程不仅要求高度一致的数据完整性,还需对光源特性、胶层响应行为及环境参数进行精细化调控。随着特征尺寸不断缩小,尤其是HDI板和IC载板对线宽/间距低于50μm的需求日益增长,传统工艺已难以满足需求,必须引入激光直写、自动对准补偿机制以及基于统计过程控制(SPC)的稳定性评估体系。本章将深入剖析光绘数据生成标准、曝光能量建模方法以及光刻胶热处理策略,并结合实际产线案例说明如何通过D-code优化、套刻误差校正和工艺能力指数分析来提升良率。

光绘机作为连接PCB设计与制造的关键桥梁,其输入依赖于标准化的图形描述文件——最广泛使用的是Gerber RS-274X格式。这一开放性标准由Ucamco公司维护,支持多层结构定义、极性控制(正负片)、Aperture属性嵌入等功能,已成为全球PCB加工厂通用的数据交换协议。然而,在实际应用中,若输出设置不当或理解偏差,极易导致短路、开路甚至阻抗不匹配等问题。因此,掌握层别定义规则、D-code配置逻辑及后处理检查手段,是确保数据可靠性的基础。

2.1.1 层别定义与输出设置(Top/Bottom Layer, Solder Mask, Silkscreen)

在EDA工具如Altium Designer中导出Gerber时,首要任务是正确映射各电路层至对应的物理功能层。典型的六层板至少包含以下关键层:

其中, Solder Mask (阻焊层)通常以“负片”方式呈现,即图形区域表示需去除阻焊油墨的位置(露出焊盘),而非图形部分保留绿油覆盖。这种表达方式能有效减少数据量并避免边缘毛刺问题。相比之下, Silkscreen (丝印层)采用正片输出,直接描绘字符、极性标记等可见信息。

在Altium Designer中的典型输出配置如下:

Output Job File: PCB.Prints

Add new output type → Gerber/Film

Layer Mapping:

- Mechanical1 → Board Outline

- Top Layer → Enabled (Unit: mm, Format: 4.6)

- Bottom Layer → Enabled

- Top Solder Mask → Polarity: Negative

- Bottom Solder Mask → Polarity: Negative

- Top Overlay → Polarity: Positive

参数说明 :

-Format: 4.6表示整数位4位、小数位6位,适用于微米级定位;

- 极性设置错误会导致焊盘被覆盖或走线暴露,引发焊接缺陷;

- 板框应单独指定至Mechanical层,避免与其他图形混淆。

此外,现代高密度互连(HDI)板常涉及盲埋孔结构,需额外输出 Drill Guide 和 Microvia Layers ,以便制造商区分不同钻孔类型。所有层别命名应遵循IPC-2581或客户指定规范,防止解析歧义。

2.1.2 D-Code解析与Aperture Table配置

D-code(Drawing Code)是Gerber文件中用于调用特定形状绘制工具的指令码,本质上是一个指向“Aperture Table”的索引。每个D-code关联一个具体的图形模板,例如圆形、矩形、八角形或多边形,决定了当前坐标的绘图行为。RS-274X格式支持内嵌Aperture定义,无需外部文件,提升了数据独立性。

一个典型的Aperture定义语法如下:

%AD10C,0.200*% ; 定义D10为直径0.2mm圆孔

%AD11R,0.150X0.300*%; 矩形,宽0.15mm高0.3mm

%AD12O,0.100X0.250*%; 八角形,外径0.1x0.25mm

随后在坐标流中调用:

D10*

X100000Y150000D02*

D01*

X105000Y150000D01*

逐行解读 :

-D10*:切换至Aperture编号10(即Φ0.2mm圆形);

-X100000Y150000D02*:移动到起点(单位为0.001inch);

-D01*:开始曝光,沿路径绘制线条;

- 坐标值采用绝对定位模式(默认),比例因子由%FSAXXXYXXX*%定义。

Aperture的选择直接影响图形保真度。例如,在细线路(<75μm)场景下,若使用过大Aperture会造成边缘模糊;而在大铜面填充时,则需合理分配Thermal Relief与Solid Pad所用D-code,防止散热不足或虚焊。

下表列出常见元件焊盘推荐Aperture配置:

在复杂设计中,建议启用“Custom Aperture”功能,利用UDA(User Defined Aperture)创建异形焊盘,如泪滴形、扇出型等,进一步增强电气可靠性。

2.1.3 光绘检查要点:短路、开路、孤立铜皮识别

完成Gerber输出后,必须执行全面的光绘前检查(DFM Check),以发现潜在制造风险。常用工具包括Ucamco的GC-Prevue、KiCad自带查看器或专业DFM软件如Valor NPI。重点核查三大类缺陷:

(1)短路检测(Short Detection)

当两个非连接网络的导体间距小于工艺极限(如常规FR-4最小间距6mil=0.1524mm)时,可能因蚀刻不足造成桥接。可通过设定Design Rule进行批量比对:

# 示例:Python脚本扫描相邻图形距离

def check_clearance(layer_data, min_gap=0.152):

for poly1 in layer_data:

for poly2 in layer_data:

if poly1.net != poly2.net:

dist = calculate_min_distance(poly1, poly2)

if dist < min_gap:

report_issue("Potential short", poly1.center, poly2.center, dist)

逻辑分析 :

- 输入为解析后的多边形列表(含网络名);

- 使用欧氏距离算法计算最近点对;

- 输出违规位置坐标及实测间隙值;

- 可集成进CI/CD流程实现自动化预警。

(2)开路检查(Open Circuit Verification)

主要关注走线中途断裂、过孔未连接、盲孔错层等问题。可通过连通性分析验证:

graph TD

A[读取Top Layer图形] --> B{是否存在孤立段?}

B -- 是 --> C[标记为潜在开路]

B -- 否 --> D[检查过孔连接性]

D --> E{Via中心是否落在走线上?}

E -- 否 --> F[报告未连接警告]

E -- 是 --> G[确认网络一致性]

(3)孤立铜皮识别(Floating Copper Detection)

指未接地或未连接电源的悬浮铜区域,易成为天线引发EMI问题。检测逻辑如下:

# 使用命令行工具dxf2svg转换后分析

gerbv --export=pdf --dpi=1200 project.gbr > preview.pdf

# 导入CAM350执行Isolated Pad Search

Run DFM Analysis → Isolated Copper → Threshold=0.5mm²

参数说明 :

- 小于0.5mm²的孤岛可忽略(视为工艺允许残铜);

- 大面积浮铜需手动添加跳线或删除;

- 特别注意BGA下方散热焊盘连接状态。

最终输出应附带一份完整的《Gerber Review Report》,包含层叠结构图、Aperture清单、最小线宽/间距统计及异常点列表,供工厂审核确认。

光刻是将掩膜版上的电路图案精确转移到感光材料(光刻胶)表面的过程,其质量直接决定后续显影与蚀刻的图形保真度。整个过程受光源性能、曝光能量、对准精度等多重因素影响,尤其在精细线路(≤50μm)制造中,任何微小波动都可能导致分辨率下降或套刻偏移。因此,建立科学的能量建模体系与误差补偿机制,是实现稳定量产的前提。

2.2.1 曝光光源类型对比:紫外汞灯 vs. 激光直写

目前主流曝光设备采用两类光源:传统高压汞灯(g-line, i-line)与新兴激光直写(Laser Direct Imaging, LDI)。两者在波长、分辨率、成本等方面存在显著差异。

传统汞灯通过滤光片提取i-line主峰,经准直透镜投射至带有图形的掩膜版,再成像于PCB表面。优点在于技术成熟、运行成本低,但受限于衍射效应,难以突破亚微米级分辨率。同时,掩膜版易磨损、变形,长期使用会导致边缘模糊。

而LDI系统采用高速振镜控制紫外激光束,依据Gerber数据实时扫描曝光,无需物理掩膜。其核心优势体现在:

- 支持动态聚焦补偿Z轴起伏;

- 可实现±2μm级别的对位精度;

- 易于集成AOI反馈形成闭环修正;

- 适合小批量多品种柔性生产。

flowchart LR

subgraph LDI System

DataInput[Gerber Input] --> LaserSource[405nm Laser Diode]

LaserSource --> GalvoMirror[XY Scanning Mirrors]

GalvoMirror --> ObjectiveLens[F-theta Lens]

ObjectiveLens --> PCB[Coated Panel]

PositionSensor[Camera Alignment] --> FeedbackControl

FeedbackControl --> GalvoDriver

end

流程说明 :

- 数据预处理模块将Gerber转换为矢量扫描路径;

- 视觉系统捕捉全局Mark点,实现粗对准;

- 激光束按像素级逐行扫描,曝光速度可达5000 mm²/s;

- 实时反馈调节镜面角度,补偿机械漂移。

尽管LDI代表未来方向,但在大批量标准板生产中,i-line曝光仍具性价比优势。选择时应综合考量产品精度等级、订单规模与交付周期。

2.2.2 曝光时间与能量密度的关系建模

曝光质量取决于到达光刻胶表面的总能量密度 $ E $(单位:mJ/cm²),其计算公式为:

E = I imes t

其中:

- $ I $:光照强度(mW/cm²)

- $ t $:曝光时间(s)

理想情况下,$ E $ 应落在光刻胶制造商提供的“工艺窗口”内。过低会导致显影不尽(残胶),过高则引起过度交联(图形收缩)。为此,需构建剂量-响应曲线模型。

实验步骤如下:

- 制备一组测试板,固定$I=10, ext{mW/cm}^2$,分别曝光$t=5, 10, 15, 20, 25, ext{s}$;

- 显影后测量线宽变化,绘制$LWR$(Line Width Roughness)曲线;

- 找出目标线宽对应的最佳$E_{opt}$。

import numpy as np

import matplotlib.pyplot as plt

# 模拟实验数据

exposure_times = np.array([5, 10, 15, 20, 25]) # seconds

intensity = 10 # mW/cm²

energy = intensity * exposure_times # mJ/cm²

measured_width = np.array([85, 78, 75, 74, 72]) # μm

# 拟合二次回归模型

coeffs = np.polyfit(energy, measured_width, 2)

fitted = np.polyval(coeffs, energy)

plt.plot(energy, measured_width, 'bo', label='Measured')

plt.plot(energy, fitted, 'r-', label='Fitted Curve')

plt.axhline(y=75, color='g', linestyle='--', label='Target 75μm')

plt.xlabel('Exposure Energy (mJ/cm²)')

plt.ylabel('Line Width (μm)')

plt.title('Energy vs Line Width Response')

plt.legend()

plt.grid(True)

plt.show()

代码解释 :

- 使用多项式拟合捕捉非线性响应趋势;

- 查找交点确定最优能量值(约120 mJ/cm²);

- 可部署至MES系统实现自动配方推荐。

在实际产线中,还需考虑面板温升引起的折射率变化,建议每2小时校准一次$I$值,并记录环境温湿度。

2.2.3 掩膜版对准精度与套刻误差补偿方法

对于多层板,每一层的图形必须与前序层保持严格对齐,否则会引起层间偏移(Misregistration),严重时导致盲孔断连或信号串扰。对准精度通常以Mark点识别为基础,分为三步:

- 粗对准 :通过CCD相机抓取全局Mark(如十字形);

- 精对准 :局部搜索微Mark(φ0.1mm圆点),亚像素级定位;

- 补偿调整 :平移、旋转、缩放(TRS模型)修正偏差。

设第$n$层相对于基准层的偏移向量为$(Δx, Δy)$,旋转角为$θ$,则变换矩阵为:

begin{bmatrix}

x’

y’

end{bmatrix}

=

begin{bmatrix}

s cdot cosθ & -s cdot sinθ

s cdot sinθ & s cdot cosθ

end{bmatrix}

begin{bmatrix}

x

y

end{bmatrix}

+

begin{bmatrix}

Δx

Δy

end{bmatrix}

其中$s$为尺度因子(通常接近1.000)。

补偿策略如下表所示:

现代高端曝光机配备自学习功能,可累积历史数据训练预测模型,提前预判热膨胀趋势并主动补偿。例如,某厂在夏季高温环境下观察到平均每小时+0.8μm热漂移,遂设置动态偏移表:

Time,Hourly_Offset_X(μm),Hourly_Offset_Y(μm)

0,0.0,0.0

1,0.6,0.7

2,1.3,1.5

3,2.1,2.0

该表导入设备控制系统后,显著降低返工率至<0.3%。

光刻胶是实现图形转移的功能性涂层,其化学组成与工艺条件共同决定了最终图形的质量。根据反应机理可分为正胶与负胶,二者在分辨率、耐蚀性及工艺适应性方面各有优劣。为最大化良率,必须围绕预烘、曝光、后烘三个阶段实施精准温控,并借助统计过程控制(SPC)工具量化工艺稳定性。

2.3.1 正胶与负胶的选择依据及分辨率差异

正胶(Positive Photoresist)在曝光区域发生链断裂,变得易溶于显影液;负胶(Negative Photoresist)则在曝光区交联固化,难溶。两者的性能对比如下:

在普通外层线路制作中,普遍采用正胶因其高分辨能力;而在厚胶应用(>50μm)如金凸块制造中,SU-8类负胶更具优势。

选择决策树如下:

graph TD

Start[选择光刻胶类型] --> Q1{线宽是否≤25μm?}

Q1 -- 是 --> UsePositive[选用正胶]

Q1 -- 否 --> Q2{是否需要厚胶电镀?}

Q2 -- 是 --> UseNegative[选用负胶]

Q2 -- 否 --> Q3{成本是否敏感?}

Q3 -- 是 --> UseStandardNegative

Q3 -- 否 --> UseHighResPositive

应用场景举例 :

- 手机主板HDI板:正胶,线宽/间距=40/40μm;

- MEMS传感器封装:SU-8负胶,厚度达100μm用于塑模;

- LED支架:负胶兼顾绝缘与反射功能。

2.3.2 预烘、曝光、后烘三阶段温控策略

光刻胶工艺“三烘一曝”流程中,温度控制极为关键:

特别是预烘阶段,若温度不足会导致溶剂残留,引起气泡或显影拖尾;过高则提前聚合,降低灵敏度。建议采用梯度升温法:

# 预烘程序脚本示例(PLC控制)

HEATER_SETPOINT = [80, 90, 95, 100] # °C

DURATION = [10, 15, 10, 15] # minutes

for temp, dur in zip(HEATER_SETPOINT, DURATION):

set_temperature(temp)

wait(dur)

log_event(f"Stage complete: {temp}°C for {dur}min")

逻辑分析 :

- 分段升温避免热冲击导致膜层开裂;

- 实时监控腔体温度,PID调节加热功率;

- 结束后自然冷却至室温再进入曝光区。

后烘主要用于深紫外(DUV)工艺中抑制驻波效应,提升侧壁垂直度。研究表明,适当后烘可使LWR改善达30%以上。

2.3.3 工艺能力指数(Cpk)在曝光稳定性评估中的应用

为量化光刻工艺的长期稳定性,引入统计指标Cpk(Process Capability Index):

Cpk = minleft(frac{USL - mu}{3sigma}, frac{mu - LSL}{3sigma}

ight)

其中:

- $USL$: 上限规格(如76μm)

- $LSL$: 下限规格(如74μm)

- $mu$: 样本均值

- $sigma$: 标准差

假设某产线连续抽取50组数据,得到$mu=75.1$, $sigma=0.3$,则:

Cpk = minleft(frac{76 - 75.1}{0.9}, frac{75.1 - 74}{0.9}

ight) = min(1.0, 1.22) = 1.0

评价标准 :

- Cpk ≥ 1.33:优秀(Six Sigma水平)

- Cpk ≥ 1.0:可接受

- Cpk < 1.0:需改进

通过每日采集Cpk趋势图,可及时发现设备老化或材料批次变异问题。例如,当Cpk连续三天下降超过15%,触发预警并启动根本原因分析(RCA)流程。

最终目标是实现Cpk ≥ 1.33的稳健制程,支撑汽车电子、医疗设备等领域对高可靠性PCB的需求。

在现代印制电路板(PCB)制造流程中,显影与蚀刻是决定线路图形精度和导电性能的核心环节。这两个步骤直接关系到最终线路的线宽控制、边缘清晰度以及是否存在短路或断路缺陷。随着高密度互连(HDI)技术的发展和微细线路(如50μm以下线宽/线距)的广泛应用,传统工艺参数已难以满足日益严苛的制程要求。因此,深入理解显影与蚀刻过程中化学反应机理、动力学行为及关键参数之间的耦合关系,成为提升良率与可靠性的关键技术突破口。

本章将从显影液组成与去胶效率模型出发,系统分析温度、时间、浓度等变量对显影效果的影响机制;继而探讨湿法蚀刻中不同蚀刻体系的选择依据、喷淋动力学对侧蚀的调控作用,并引入“蚀刻因子”作为量化评估线路保真度的重要指标;最后结合去膜清洗与抗氧化处理,构建完整的线路保护闭环策略。通过建立可量化的数学模型、可视化流程图以及实际操作代码模拟,为工艺工程师提供理论支持与实践指导。

显影是光刻后将曝光区域的光刻胶去除的关键步骤,其本质是一个基于碱性溶液与感光树脂发生水解反应的化学溶解过程。对于正性光刻胶而言,曝光区域因分子链断裂而生成羧酸基团,在碱性环境中形成可溶性盐类物质,从而被冲洗掉;未曝光区域则保持不溶状态,形成所需的抗蚀图形。该过程不仅依赖于显影液的化学组成,还受到温度、时间、搅拌强度等多种物理条件的共同影响。

为了实现高效且均匀的显影效果,必须精确控制各参数之间的协同关系。尤其是在多层板或高密度布线结构中,局部显影不足可能导致残留胶体引发后续蚀刻异常,而过度显影又会造成图形边缘模糊甚至桥接短路。因此,建立一个能够预测去胶速率与残留膜厚的动力学模型,具有重要的工程价值。

3.1.1 显影液成分组成:Na₂CO₃浓度与表面活性剂配比

显影液的主要成分为碳酸钠(Na₂CO₃),其作用是提供碱性环境以促进光刻胶中酚醛树脂的去质子化反应:

ext{R-OH} + ext{OH}^-

ightarrow ext{R-O}^- + ext{H}_2 ext{O}

其中 R-OH 代表未曝光的树脂单元,而在曝光区,由于光敏剂产酸催化交联或断链,使得部分结构更容易被 OH⁻ 攻击并溶解。Na₂CO₃ 水解产生 OH⁻ 离子:

ext{Na}_2 ext{CO}_3 + ext{H}_2 ext{O}

ightleftharpoons 2 ext{Na}^+ + ext{HCO}_3^- + ext{OH}^-

因此,Na₂CO₃ 浓度直接影响溶液 pH 值与游离 OH⁻ 含量。实验表明,当浓度低于 0.5 wt% 时,显影速度过慢,易出现残胶;超过 2.0 wt% 则可能引起非选择性腐蚀,导致图形失真。

此外,添加适量的非离子型表面活性剂(如 Triton X-100 或 Surfynol 465)可显著改善润湿性能,减少气泡附着,提高显影液在细微线路间的渗透能力。但过量添加会降低表面张力过多,造成雾状残留或“拖尾”现象。

下表列出了典型显影液配方及其适用场景:

# Python 示例:计算不同 Na2CO3 浓度下的理论 pH 值(简化模型)

import numpy as np

def calculate_ph(na2co3_concentration_wt):

# 假设密度 ≈1 g/mL,摩尔质量 = 106 g/mol

mol_per_L = (na2co3_concentration_wt / 100) * 10 / 106 # mol/L

# CO3^2- 水解常数 Kb1 ≈ 2.1e-4

kb1 = 2.1e-4

oh_concentration = np.sqrt(kb1 * mol_per_L)

pOH = -np.log10(oh_concentration)

return 14 - pOH

# 计算 0.5~2.0 wt% 范围内 pH 变化

concs = np.linspace(0.5, 2.0, 6)

ph_values = [calculate_ph(c) for c in concs]

print("Na2CO3 浓度 (wt%) vs. 预计 pH:")

for c, ph in zip(concs, ph_values):

print(f"{c:.1f}% → pH {ph:.2f}")

代码逻辑逐行解析:

- 第 3–7 行:定义函数

calculate_ph,输入为 Na₂CO₃ 质量百分比浓度。 - 第 5 行:将 wt% 转换为 mol/L,假设溶液密度为 1 g/mL,便于近似计算。

- 第 8 行:使用弱碱水解公式 $[ ext{OH}^-] = sqrt{K_b cdot C}$,忽略二级水解。

- 第 9–10 行:由 [OH⁻] 推出 pOH 和 pH。

- 第 13–17 行:在 0.5–2.0 wt% 范围内取 6 个点进行测试,输出对应 pH。

参数说明:

- kb1 = 2.1e-4 是 CO₃²⁻ 的第一级水解常数,适用于室温条件。

- 实际应用中需考虑温度补偿与离子强度修正,此处仅为教学演示。

该模型可用于初步判断显影液碱性强弱,辅助设定初始浓度范围。

3.1.2 温度-时间耦合效应下的去胶效率模型

显影效率不仅取决于化学成分,更受热力学与传质过程支配。升高温度可加速分子运动,增强 OH⁻ 向胶层内部扩散的能力,缩短达到完全去除所需的时间。然而,温度过高(>35°C)会导致显影液蒸发加剧、pH 不稳定,甚至引发胶层起皱或剥离。

研究表明,显影速率遵循阿伦尼乌斯方程形式:

r(T,t) = r_0 cdot e^{-E_a / RT} cdot (1 - e^{-kt})

其中:

- $ r $:单位时间内去除的胶厚(μm/min)

- $ E_a $:活化能(约 45–60 kJ/mol 对于酚醛树脂)

- $ R $:气体常数(8.314 J/mol·K)

- $ T $:绝对温度(K)

- $ t $:显影时间(min)

- $ k $:一级反应速率常数,与搅拌速度相关

为直观展示温度与时间的耦合作用,绘制如下 Mermaid 流程图 描述自动显影控制系统的工作逻辑:

graph TD

A[开始显影] --> B{设定目标线宽?}

B -->|是| C[读取工艺配方]

C --> D[设置温度: 28±1°C]

D --> E[调整Na2CO3浓度: 1.0wt%]

E --> F[启动传送带, 速度=1.2m/min]

F --> G[在线监测pH与温度]

G --> H{是否偏离设定值?}

H -->|是| I[反馈调节加热/补液]

H -->|否| J[持续显影30-60秒]

J --> K[进入漂洗槽]

K --> L[完成显影]

此流程体现了现代显影设备中的闭环控制思想,确保每一批次的一致性。

进一步地,可通过实验数据拟合得到经验公式:

D(t,T) = D_{max} left(1 - e^{-0.045 cdot t cdot e^{(T - 25)/10}}

ight)

其中 $ D $ 为去胶厚度(μm),$ D_{max} $ 为初始胶厚(通常为 1.2–2.0 μm)。该式表明,每升高 10°C,反应速率大致翻倍。

3.1.3 显影均匀性检测:边缘清晰度与残留膜厚测量

显影后的图形质量需通过多种手段验证。常用方法包括:

- 显微图像分析法 :利用金相显微镜或扫描电子显微镜(SEM)观察线路边缘锐利程度,是否存在“ undercut ”或“ footing ”现象;

- 椭偏仪测量残留膜厚 :对未完全去除的区域进行纳米级厚度检测;

- 反射率对比法 :基于铜面与残留胶的反光差异,采用自动光学检测(AOI)系统识别异常区域。

下面是一个基于 OpenCV 的 Python 脚本示例,用于提取显影后图像的边缘清晰度评分:

import cv2

import numpy as np

# 加载显影后 PCB 表面灰度图

image = cv2.imread('developed_pcb.jpg', cv2.IMREAD_GRAYSCALE)

# 使用 Sobel 算子检测水平与垂直梯度

grad_x = cv2.Sobel(image, cv2.CV_64F, 1, 0, ksize=3)

grad_y = cv2.Sobel(image, cv2.CV_64F, 0, 1, ksize=3)

# 计算总梯度幅值

gradient_magnitude = np.sqrt(grad_x**2 + grad_y**2)

# 计算平均梯度值作为“边缘清晰度”指标

sharpness_score = np.mean(gradient_magnitude)

print(f"边缘清晰度评分: {sharpness_score:.2f} (越高越清晰)")

# 输出二值化边缘图用于人工复核

_, edges = cv2.threshold(gradient_magnitude, 50, 255, cv2.THRESH_BINARY)

cv2.imwrite('edge_detection_result.png', edges)

代码逻辑逐行解读:

- 第 3 行:读取一张显影后的 PCB 图像,转为灰度图以便处理。

- 第 6–7 行:使用 Sobel 算子分别检测 X 和 Y 方向的强度变化率,反映边缘陡峭程度。

- 第 10 行:合成总梯度幅度,数值越大表示边缘越明显。

- 第 13 行:取全图平均梯度作为整体“清晰度”评分。

- 第 17–18 行:生成二值边缘图供质检人员查看。

参数说明:

- ksize=3 表示 Sobel 卷积核大小,适合检测细微边缘。

- 若图像噪声较多,建议先进行高斯滤波( cv2.GaussianBlur )预处理。

该方法可集成至 AOI 系统中,实现实时质量监控。

蚀刻是将裸露的铜层通过化学或电化学方式选择性去除的过程,目的是保留由干膜或湿膜保护的线路部分。理想的蚀刻应具备高度的各向异性——即只沿垂直方向进行,避免横向扩散造成“侧蚀”,否则会导致线宽缩小、阻抗偏差甚至开路故障。

目前主流采用的是喷淋式湿法蚀刻,其均匀性优于浸泡式,尤其适用于大尺寸面板。然而,喷嘴布局、压力分布、传输速度等因素若控制不当,极易引起蚀刻不均或局部欠蚀。

3.2.1 湿法蚀刻液体系:氯化铁、酸性氯化铜与碱性氨水比较

常用的三种蚀刻液体系特性对比如下表所示:

从反应机理看,酸性体系主要依赖氧化还原反应:

ext{Cu} + 2 ext{Fe}^{3+}

ightarrow ext{Cu}^{2+} + 2 ext{Fe}^{2+}

而在氯化铜体系中,Cu²⁺ 直接参与反应:

ext{Cu} + ext{Cu}^{2+} + 4 ext{Cl}^-

ightarrow 2[ ext{CuCl}_2]^-

随后通过空气氧化再生:

4[ ext{CuCl}_2]^- + O_2 + 4H^+

ightarrow 4 ext{Cu}^{2+} + 4Cl^- + 2H_2O

这使得酸性氯化铜系统可循环使用,大幅降低废液排放。

相比之下,碱性氨水体系通过络合溶解:

ext{Cu} + 4 ext{NH}_3 + frac{1}{2} ext{O}_2} + ext{H}_2 ext{O}

ightarrow [ ext{Cu(NH}_3)_4]^{2+} + 2 ext{OH}^-

因其反应温和,侧蚀较小,特别适用于精细线路(<75μm)加工。

3.2.2 喷淋压力与传输速度对侧蚀率的影响

喷淋系统的动力学参数直接影响蚀刻均匀性。喷嘴压力决定了液流冲击力和穿透能力,而传输速度则决定了基板在蚀刻区的停留时间。

设侧蚀宽度为 $ W_l $,垂直蚀刻深度为 $ D_v $,则侧蚀率定义为:

ext{Lateral Etch Rate} = frac{W_l}{D_v}

理想值应小于 0.2,即每向下蚀刻 1μm,横向扩展不超过 0.2μm。

实验数据显示,喷淋压力与传输速度的关系如下:

import matplotlib.pyplot as plt

pressures = [1.0, 1.5, 2.0, 2.5, 3.0] # bar

speeds = [1.0, 1.2, 1.4, 1.6, 1.8] # m/min

lateral_rates = [[0.35, 0.30, 0.28, 0.32, 0.38],

[0.28, 0.25, 0.24, 0.26, 0.30],

[0.25, 0.22, 0.20, 0.23, 0.27],

[0.27, 0.24, 0.23, 0.25, 0.29],

[0.30, 0.28, 0.27, 0.30, 0.34]]

plt.contourf(speeds, pressures, lateral_rates, levels=15, cmap='coolwarm')

plt.colorbar(label='侧蚀率')

plt.xlabel('传输速度 (m/min)')

plt.ylabel('喷淋压力 (bar)')

plt.title('喷淋压力与传输速度对侧蚀率的影响')

plt.show()

图表解释:

- 中间区域(压力 2.0 bar,速度 1.4 m/min)达到最低侧蚀率(0.20),为最佳工艺窗口。

- 压力过低则冲击不足,导致底部蚀刻不彻底;过高则扰动加剧,反而增加横向扩散。

- 速度过快则接触时间不足,欠蚀;过慢则延长暴露时间,加剧侧蚀。

3.2.3 蚀刻因子(Etch Factor)计算与线路保真度提升

蚀刻因子(Etch Factor, EF)是衡量蚀刻质量的重要指标,定义为:

EF = frac{ ext{基底铜厚}}{2 imes ext{侧蚀宽度}}

例如,原始铜厚为 35 μm,侧蚀宽度为 5 μm,则:

EF = frac{35}{2 imes 5} = 3.5

一般认为 EF > 3 为合格,EF > 5 表示优异的各向异性。

为提升 EF,可采取以下措施:

- 优化喷嘴角度与排列密度 :采用交错双排喷嘴,增强背面冲洗能力;

- 添加抑制剂 :如聚乙二醇(PEG),优先吸附于侧壁,减缓横向反应;

- 脉冲喷淋模式 :周期性启停喷嘴,避免连续冲刷引起的湍流扩散。

flowchart LR

Start[开始蚀刻] --> A[检查铜厚与图形密度]

A --> B[选择蚀刻液类型]

B --> C[设定喷淋压力: 2.0 bar]

C --> D[调节传输速度: 1.4 m/min]

D --> E[启用脉冲喷淋模式]

E --> F[实时监测出口铜离子浓度]

F --> G{是否超出阈值?}

G -->|是| H[自动补加新鲜蚀刻液]

G -->|否| I[继续运行]

I --> J[完成蚀刻,进入清洗]

该流程展示了智能蚀刻线的自适应控制逻辑,有助于维持稳定 EF 值。

显影与蚀刻完成后,必须彻底清除剩余的抗蚀干膜或湿膜,以防残留物影响后续沉铜、电镀或焊接性能。去膜不仅是清洁过程,更是保障线路完整性的重要环节。

3.3.1 剥离液选择与环保处理要求

常用剥离液包括:

- 强碱类:如 NaOH(5–10%),适用于大多数丙烯酸系干膜;

- 有机溶剂类:如二甲基亚砜(DMSO)、N-甲基吡咯烷酮(NMP),溶解能力强;

- 复合型剥离剂:含表面活性剂与缓蚀剂,兼顾效率与基材保护。

环保方面,NMP 被列为 SVHC 物质(高关注化学品),需严格回收;NaOH 废液需中和至 pH 6–9 后方可排放。

推荐绿色替代方案:基于植物提取物的生物降解型剥离液,虽成本较高,但符合 RoHS 与 REACH 法规。

3.3.2 去膜后清洗流程:超声波辅助与纯水冲洗标准

标准清洗流程如下:

- 预洗 :热水(50–60°C)冲洗,软化残留膜;

- 超声波清洗 :频率 40 kHz,时间 3–5 分钟,有效去除盲孔内残留;

- 三级逆流漂洗 :使用电阻率 ≥15 MΩ·cm 的去离子水;

- 热风烘干 :80–100°C,避免水渍残留。

清洗效果可通过“水破测试”(Water Break Test)验证:清洁表面应形成连续水膜,无破裂或珠状聚集。

3.3.3 线路氧化防护:临时抗氧化涂层喷涂技术

裸铜线路极易氧化,特别是在高温高湿环境下。为防止氧化影响可焊性,常采用临时保护措施:

- OSP(有机保焊膜):形成单分子层氮杂环化合物,厚度 0.2–0.5 μm;

- 苯并三氮唑(BTA)喷涂:与铜形成稳定络合物,防变色能力强;

- 微薄助焊剂涂层:兼具保护与助焊功能,适用于快速组装场景。

喷涂参数需精准控制:

综上所述,显影与蚀刻并非孤立工序,而是涉及化学、流体力学、材料科学与自动控制的复杂系统工程。唯有通过精细化建模、实时监测与闭环优化,才能在高产能下实现一致性的高品质输出。

在现代高密度互连(HDI)印刷电路板(PCB)制造中,孔结构不仅是实现层间电气连接的关键通道,更是决定整板可靠性和信号完整性的核心环节。随着电子设备向小型化、高频高速方向发展,对微孔、盲埋孔及通孔的加工精度、孔壁质量与金属化一致性提出了前所未有的挑战。本章系统阐述从机械钻孔到激光打孔,再到化学镀铜与电镀增厚的全流程关键技术控制点,聚焦于高精度钻孔工艺、孔壁活化机制优化以及电镀均匀性保障等关键环节。通过深入分析材料选择、设备参数调控、化学反应动力学和电流场分布建模,揭示影响孔金属化质量的根本因素,并提出可落地的工艺改进方案。

钻孔作为PCB制造中最早引入三维结构的工序,直接决定了后续金属化通孔的质量基础。无论是传统的机械钻孔还是新兴的激光钻孔技术,其加工精度、孔壁粗糙度、毛刺控制及层间对准能力均需严格受控。尤其在多层板层数不断增加、线宽线距持续缩小的趋势下,任何微小的孔位偏差或孔径不一致都可能导致后续电镀短路、开路或阻抗异常等问题。

4.1.1 钻头材质与寿命管理:碳化钨磨损监测

目前主流PCB钻孔仍以硬质合金(碳化钨,WC-Co)钻头为主,因其具备较高的硬度(HV 1500~2000)、良好的耐磨性与热稳定性,适用于FR-4、高频材料(如Rogers)等多种基材。然而,在连续高速旋转(通常3万~6万转/分钟)与高压进给条件下,钻头刃口会因摩擦发热、树脂粘连和玻璃纤维冲击而逐渐磨损,导致孔径缩小、排屑不畅甚至断针。

为实现稳定生产,必须建立完善的钻头寿命管理体系。常用策略包括:

- 按孔数设定更换周期 :例如每钻5000~8000个孔强制更换;

- 在线监控振动与电流信号 :利用主轴电机负载变化判断刃口钝化程度;

- 定期显微镜检测刃口形貌 :观察崩刃、积瘤等缺陷。

graph TD

A[新钻头安装] --> B{是否首次使用?}

B -- 是 --> C[空转校正同心度]

B -- 否 --> D[读取历史使用记录]

D --> E[计算剩余寿命]

E --> F{寿命<10%?}

F -- 是 --> G[标记待换]

F -- 否 --> H[投入生产]

H --> I[实时采集电流/振动数据]

I --> J{波动>阈值?}

J -- 是 --> K[暂停并检查]

J -- 否 --> L[继续加工]

该流程图展示了基于状态感知的智能钻头管理逻辑,通过融合设备传感器数据与MES系统信息,实现预测性维护,显著降低非计划停机率。

代码示例:钻头磨损趋势分析脚本(Python)

import numpy as np

import matplotlib.pyplot as plt

from scipy.stats import linregress

# 模拟采集的钻头使用数据:孔数 vs 直径偏差

hole_count = np.array([1000, 2000, 3000, 4000, 5000, 6000, 7000])

diameter_error = np.array([+1.2, +2.1, +3.5, +5.0, +7.2, +9.8, +13.5]) # μm

# 线性回归拟合磨损速率

slope, intercept, r_value, p_value, std_err = linregress(hole_count, diameter_error)

predicted_life = (15 - intercept) / slope # 设定报废临界为15μm

print(f"磨损斜率: {slope:.3f} μm/千孔")

print(f"预测寿命: 孔")

plt.plot(hole_count, diameter_error, 'bo-', label='实测偏差')

plt.axhline(y=15, color='r', linestyle='--', label='报废阈值')

plt.plot(hole_count, slope * hole_count + intercept, 'g--', label='趋势线')

plt.xlabel("累计钻孔数量")

plt.ylabel("直径偏差 (μm)")

plt.title("碳化钨钻头磨损趋势分析")

plt.legend()

plt.grid(True)

plt.show()

逻辑分析与参数说明:

-

hole_count:表示已加工的孔总数,单位为“个”,按千计便于可视化。 -

diameter_error:实际测量得到的钻孔直径相对于标称值的正偏差,反映刃口磨损导致的“扩孔”效应。 - 使用

linregress进行最小二乘法拟合,得出磨损速率(斜率),可用于预测何时达到最大允许误差(如15μm)。 - 图表输出帮助工艺工程师直观判断是否需要提前更换刀具,避免批量不良。

此方法可集成至工厂SCADA系统,自动触发报警或调度换刀任务,提升制程稳定性。

4.1.2 孔位偏差来源分析:层间偏移、机械振动抑制

尽管现代数控钻床定位精度可达±2μm以内,但在实际多层板加工中,常见孔位偏差仍可能达到±30~50μm,严重影响后续压合对准与电镀连通性。主要偏差源可分为三类:

-

材料变形引起的层间错位(Lamination Shift)

多层板在压合过程中由于树脂流动、温度梯度不均等原因造成内层板发生轻微滑移,导致钻孔时参考基准失准。 -

设备机械系统误差

包括导轨间隙、丝杠反向间隙、伺服响应延迟、主轴热伸长等,特别是在长时间运行后累积误差明显。 -

外部干扰因素

如地基振动、空气压缩波动、冷却水温变化等环境扰动,影响平台稳定性。

为量化控制这些影响,建议采用 靶标测试板(Test Coupon) 进行统计过程控制(SPC)。典型做法是在拼版边缘设置多个同心圆靶标,钻孔后用X-ray检测系统测量各层中心偏移量,计算总偏移矢量。

# 计算二维孔位偏移矢量(X, Y)

def calculate_offset(x1, y1, x2, y2):

dx = x2 - x1

dy = y2 - y1

magnitude = np.sqrt(dx**2 + dy**2)

angle = np.arctan2(dy, dx) * 180 / np.pi

return magnitude, angle

# 示例数据:某孔在顶层与底层的实际坐标

top_x, top_y = 10000.5, 20000.3 # 单位:μm

bot_x, bot_y = 10002.1, 20001.7

offset_mag, offset_ang = calculate_offset(top_x, top_y, bot_x, bot_y)

print(f"层间偏移量: μm, 方向: °")

逐行解读:

- 定义函数

calculate_offset,输入上下两层坐标的(X,Y),返回偏移大小与角度; - 使用欧几里得距离公式计算偏移模长;

-

np.arctan2(dy, dx)可正确处理四个象限的角度; - 输出结果用于评估是否超出IPC-6012规定的最大层间偏移限值(一般≤75μm)。

结合上述方法,可通过调整压合参数(如真空压力曲线)、优化钻床地脚减震装置、实施每日首件X-ray验证等方式有效控制孔位精度。

4.1.3 微孔与盲埋孔加工技术演进(Laser Drilling应用)

随着HDI板广泛应用,传统机械钻孔难以满足<100μm微孔需求,激光钻孔成为主流解决方案。主要有三种类型:

其中,UV激光因其短波长、高峰值功率和冷加工特性,广泛用于制作盲孔(Blind Via)和埋孔(Buried Via)。其工作原理是通过高能光子打断分子键实现“光蚀”而非熔融去除材料,从而获得更光滑的孔壁和更小的热影响区。

典型的激光钻孔流程如下:

flowchart LR

A[叠层板清洗] --> B[覆盖PI膜或干膜]

B --> C[激光编程定位]

C --> D[逐层打孔]

D --> E[去膜清理]

E --> F[等离子除胶]

F --> G[进入化学镀铜流程]

值得注意的是,激光打孔后常残留碳化物或“重铸层”(Recast Layer),必须通过等离子体处理(O₂/CF₄混合气体)彻底清除,否则将严重影响化学镀铜的附着力。

此外,为提高效率,现代设备普遍采用 阶梯式打孔(Staggered Drilling) 和 多光束并行加工 技术。例如一台六头UV激光机可在同一时间内完成六个区域的同步钻孔,产能提升达5倍以上。

综上所述,高精度钻孔不仅是物理成型过程,更是涉及材料科学、机械工程与自动化控制的综合性工艺。唯有通过对工具寿命、设备状态与加工路径的全面监控,才能确保每一孔都成为可靠电气连接的基础。

完成钻孔后的PCB板需经历一系列前处理与表面改性步骤,方能实现非导体孔壁的有效金属化。其中最关键的是 孔壁活化 与 化学镀铜 两个环节,它们共同决定了最终通孔的导电性、结合强度与长期可靠性。若处理不当,极易出现“空洞”、“漏镀”或“起泡”等致命缺陷。

4.2.1 前处理工序:除胶渣与中和还原流程

钻孔过程中高温会使环氧树脂碳化并附着于孔壁形成“胶渣”(Smear),阻碍后续金属沉积。因此必须进行 除胶渣(Desmear) 处理,常用方法有:

- 浓硫酸处理 :适用于FR-4,浓度93%~98%,温度50~70℃,时间5~10分钟;

- 高锰酸钾碱性氧化法 :对聚酰亚胺等耐热材料更有效;

- 等离子体清洗 :环保且无死角,适合复杂结构HDI板。

除胶后还需进行 中和还原 ,以去除残余氧化剂并恢复表面活性。典型流程如下:

此阶段特别注意水流速度与喷淋覆盖率,防止局部残留引发后续镀层剥离。

4.2.2 胶体钯活化机制与敏化-活化双步法优化

为了使绝缘的孔壁能够启动自催化化学镀铜反应,必须预先吸附具有催化活性的金属粒子——最常用的是 胶体钯(Palladium Colloid) 。

传统工艺采用“ 敏化-活化双步法 ”:

- SnCl₂敏化 :使孔壁吸附二价锡离子(Sn²⁺);

- PdCl₂活化 :Sn²⁺还原Pd²⁺生成Pd⁰核,形成胶体团簇。

反应式如下:

ext{Sn}^{2+} + ext{Pd}^{2+}

ightarrow ext{Sn}^{4+} + ext{Pd}^0 downarrow

但该方法存在稳定性差、钯利用率低的问题。为此,行业逐步推广 直接吸附法 (Direct Bonding Process, DBP),即使用有机载体将钯离子直接锚定在孔壁,省去锡盐中间层,减少污染风险。

对比表格如下:

4.2.3 化学镀铜层厚度控制(0.5~1μm)与附着力测试

化学镀铜(Electroless Copper Plating)是一种无需外加电流的自催化沉积过程,依赖甲醛作为还原剂,在Pd催化位点上析出金属铜:

ext{Cu}^{2+} + 2 ext{HCHO} + 4 ext{OH}^- xrightarrow{ ext{Pd}} ext{Cu}^0 downarrow + 2 ext{HCOO}^- + 2 ext{H}_2鷫ow + 2 ext{H}_2 ext{O}

关键控制参数包括:

- pH值:维持在11.0~11.8之间;

- 温度:65~70℃;

- [Cu²⁺]:2.5~3.5 g/L;

- 甲醛浓度:4~6 mL/L;

- 稳定剂(如CN⁻):防止自发分解。

镀层厚度通常控制在0.5~1.0μm,足以支撑后续电镀种子层。过厚会导致成本上升且易产生内应力裂纹。

验证附着力的标准方法是 热应力试验+横截面金相观察 。即将样品浸入288℃锡炉10秒,重复三次后切片观察是否有孔壁分离现象。合格标准为无鼓包、无分层。

pie

title 化学镀铜失败原因分布

“活化不足” : 35

“前处理不净” : 25

“药水老化” : 20

“温度失控” : 15

“其他” : 5

由此可见,前处理与活化是决定成败的核心环节,必须严格执行SOP并定期做能力验证(Process Capability Validation)。

化学镀铜仅提供薄导电层,真正承担大电流传输功能的是后续的 电镀铜 (Electrolytic Copper Plating)。该工序要求在通孔内部均匀沉积20~25μm厚的铜层,同时兼顾表面线路的共镀,是一项极具挑战的传质-电流传导耦合问题。

4.3.1 电流密度分布仿真与阳极布局设计

由于通孔深宽比(Aspect Ratio)可达10:1甚至更高,孔口与孔底的电流密度差异极大,容易出现“狗骨头”(Dog-bone)现象——即孔口铜厚远大于孔中和孔底。

解决之道在于优化 阳极布置 与 电流波形控制 。常用手段包括:

- 使用可调距阳极板,靠近阴极侧增加屏蔽环;

- 采用脉冲反向电镀(PRC)技术,周期性反转电流方向以抑制边缘堆积;

- 添加整平剂(Leveler)优先吸附于高电流区,抑制过度沉积。

借助COMSOL或Ansys Q3D等软件进行 电流传导场仿真 ,可提前预测镀层分布趋势。以下为简化模型代码框架(MATLAB风格):

% 简化电镀仿真:一维泊松方程求解

L = 200e-6; % 孔深 200μm

Nx = 100; % 空间离散点数

dx = L / Nx;

x = linspace(0, L, Nx);

% 初始边界条件

J_surface = 2.5; % mA/cm²

D = 1e-5; % 扩散系数 cm²/s

zeta = 0.8; % 传递系数

% 计算相对沉积速率分布

rate = J_surface * exp(-x * 0.01); % 经验衰减模型

plot(x*1e6, rate, 'LineWidth', 2)

xlabel('孔深 (mum)')

ylabel('相对沉积速率')

title('电镀铜沿孔深分布趋势')

grid on

参数说明:

-

J_surface:表面电流密度,受槽液导电性与电压影响; -

exp(-x * 0.01):模拟电流随深度指数衰减; - 输出图形显示孔口沉积快,底部缓慢,符合实际观测。

真实三维模型需考虑孔口边缘“尖端效应”、添加剂吸附动力学等复杂因素,但此简模已可用于初步工艺评估。

4.3.2 添加剂体系(载体、光亮剂、抑制剂)作用机理

现代酸性硫酸铜电镀液包含三大功能性添加剂:

其协同作用可用“ 抑制-去抑制模型 ”解释:载体与抑制剂在孔口形成致密吸附层,强烈抑制铜沉积;而光亮剂携带正电荷,能穿透吸附层并在低电流区(如孔底)促进成核,从而实现“自整平”。

实时监控添加剂浓度常采用 循环伏安扫描 stripping (CVS) 技术,通过测定特征峰电流变化反推各组分含量,确保配方稳定。

4.3.3 通孔镀层“狗骨头”现象成因与解决方案

“狗骨头”指孔口两侧铜层异常增厚,形似骨头两端膨大,严重时会引起阻焊层破裂或焊接应力集中。

主要原因包括:

- 电流集中于孔口边缘;

- 添加剂消耗不均;

- 溶液搅拌不足导致扩散受限。

应对措施:

- 优化电镀夹具设计 :增加挡板或弧形遮蔽片;

- 采用周期换向电镀 (PC/PRC);

- 提高溶液循环流速 (≥2 m/s);

- 引入超声辅助电镀 ,增强微观传质。

最终通过 X-ray断层扫描 或 微切片分析 确认孔内铜厚分布是否满足IPC-TM-650 2.6.26标准(最小厚度≥18μm,变异系数<15%)。

综上,从钻孔到金属化的全过程是一个高度协同的系统工程,每一个环节的微小偏差都会被层层放大。唯有依靠精密设备、科学药水管理和先进检测手段,才能打造出高性能、高可靠的互连结构,支撑未来智能化电子系统的持续演进。

PCB在完成金属化和线路成型后,裸露的铜表面极易氧化,影响焊接可靠性与长期稳定性。因此,选择合适的表面处理工艺是确保可焊性、存储稳定性及后续SMT贴装成功的关键环节。目前主流的表面处理技术包括OSP(Organic Solderability Preservative)、ENIG(Electroless Nickel Immersion Gold)、沉银(Immersion Silver, AgCN)和沉锡(Immersion Tin)等,其选型需综合考虑成本、工艺兼容性、热稳定性及最终应用场景。

5.1.1 OSP有机保焊膜:成膜厚度与热稳定性测试

OSP是一种水溶性有机化合物,通过化学方式吸附于裸铜表面形成一层均质保护膜,厚度通常控制在0.2~0.5μm之间。该工艺成本低、环保且支持多次回流焊,但对存储环境敏感。

# 示例:OSP膜厚检测操作流程(XRF法)

1. 样品准备:取3个不同区域的测试点(中心、边缘、BGA区域)

2. 使用X射线荧光光谱仪(XRF)测量Cu信号衰减强度

3. 软件自动计算等效有机膜厚

4. 判定标准:0.3 ± 0.1 μm,超出范围则判定为涂覆不均

热稳定性测试常采用 耐热冲击实验 :

- 条件:260°C锡炉浸渍10秒,重复3次

- 检查项目:起泡、变色、润湿不良

- 合格标准:润湿面积 > 95%,无明显退膜现象

5.1.2 ENIG化学镍金工艺:磷含量控制与黑盘缺陷防范

ENIG通过化学镀镍(Ni-P合金,厚度3~7μm)后再置换沉积薄金层(0.05~0.1μm),提供优异的平整度与长期抗氧化能力,广泛用于BGA、高频器件封装。

关键参数控制如下表所示:

“黑盘”(Black Pad)是ENIG典型失效模式,表现为镍层表面局部腐蚀导致焊点虚接。其成因多为过度浸金或清洗不足。预防措施包括:

- 缩短浸金时间至≤3分钟

- 引入中间冲洗步骤(DI水喷淋)

- 采用SEM+EDS进行截面元素分析验证

5.1.3 沉银(AgCN)与沉锡工艺的存储条件要求

沉银利用氰化物体系在铜表面沉积0.1~0.3μm银层,具有优良的共面性和高频性能,但易受硫化物污染发黑。推荐存储条件为:

- 温度:20±5°C

- 湿度:<60% RH

- 包装:防静电铝箔袋 + 干燥剂 + O₂吸收剂

- 存储期限:开封后≤12小时投入SMT

沉锡适用于无铅焊接,锡层厚度约0.8~1.2μm,但存在“锡须”生长风险。建议添加少量铅(<0.1%)或采用再流处理抑制晶须,并避免高温高湿环境长期存放。

5.2.1 阻焊油墨涂覆方式:丝网印刷 vs. 喷印

阻焊层(Solder Mask)用于防止焊接短路并提高绝缘性能。两种主流涂覆方式对比见下表:

喷印技术通过压电喷头将液态阻焊油墨精确喷射到指定区域,无需制作网版,特别适合小批量多品种生产。

5.2.2 固化曲线设定:UV曝光与热固化联合作用

阻焊油墨需经历预烘、曝光、后固化三阶段。典型固化工艺窗口如下:

graph LR

A[预烘: 75°C × 30min] --> B[UV曝光: 500~800 mJ/cm²]

B --> C[热固化: 150°C × 60min]

C --> D[硬度达标: ≥6H铅笔测试]

其中UV能量密度使用辐射计定期校准,偏差不得超过±10%。若能量不足会导致显影残留;过高则引起油墨脆裂。

5.2.3 元件标识清晰度标准与AI视觉识别适配

丝印字符用于元器件定位与追溯,常用字体为Helvetica或OCR-B,高度≥1.0mm。清晰度检测采用AI视觉系统自动判读,评分标准如下:

现代AOI设备已集成OCR模块,可在分板前完成标签读取并与MES系统比对,实现全程可追溯管理。

5.3.1 飞针测试与专用夹具测试适用场景对比

电气连通性测试是出厂前最后一道防线。两种主要测试方式如下:

对于年产量低于5,000片的订单,优先采用飞针测试以降低NRE成本。

5.3.2 AOI自动光学检测算法对微短路识别能力

AOI系统通过多角度彩色光源与高分辨率相机采集图像,结合机器学习算法识别缺陷。针对线宽/间距≤100μm的高密度板,采用以下增强策略:

# 伪代码:基于边缘梯度的微短路检测算法

def detect_micro_short(image):

gray = cv2.cvtColor(image, cv2.COLOR_BGR2GRAY)

blur = cv2.GaussianBlur(gray, (3,3), 0)

edges = cv2.Canny(blur, 50, 150, apertureSize=3)

# 查找相邻走线间异常桥接

kernel = np.ones((1,3), np.uint8)

dilated_edges = cv2.dilate(edges, kernel, iterations=1)

contours, _ = cv2.findContours(dilated_edges, cv2.RETR_EXTERNAL, cv2.CHAIN_APPROX_SIMPLE)

for cnt in contours:

if cv2.contourArea(cnt) < MIN_AREA_THRESHOLD:

continue

x,y,w,h = cv2.boundingRect(cnt)

aspect_ratio = w/h

if aspect_ratio > 5: # 细长桥接特征

report_defect(x, y, w, h, "Potential Micro-short")

当前先进AOI设备可检出最小短路长度达20μm,误报率控制在<0.5%。

5.3.3 分板方式选择:V-cut、冲模、激光切割经济性评估

分板工艺直接影响边缘质量与生产效率。三种主流方式经济性对比如下:

激光切割虽成本高,但支持异形轮廓与超窄间隙,适合HDI板与柔性板加工。

5.3.4 IPC-A-600验收标准与ROHS/REACH环保合规审核流程

依据IPC-A-600G标准,PCB外观检验分为目标、可接受、不合格三级。关键检查项包括:

- 导体宽度缩减 ≤10%

- 钻孔偏移 ≤0.1mm

- 阻焊覆盖焊盘边缘 ≥0.05mm

- 分层/起泡 零容忍

环保合规方面,企业需建立材料声明数据库(MDR),并通过第三方实验室进行SVHC筛查。典型检测项目包括:

所有批次出货前必须附带符合性声明(DoC),并上传至客户供应链平台完成闭环审核。

本文还有配套的精品资源,点击获取

简介:PCB(印刷电路板)是电子设备中的核心组件,其制造过程涉及设计、光绘、蚀刻、钻孔、镀铜、表面处理及测试等多个精密步骤。每个环节都直接影响产品的性能与可靠性。本文系统介绍了PCB板的完整工艺流程,涵盖从电路设计到最终切割封装的关键技术要点,强调质量控制与环保要求,帮助读者全面掌握PCB生产的核心原理与实际操作规范。

本文还有配套的精品资源,点击获取