生物钉是什么材料【信息科学与工程学】计算机科学与自动化——第十六篇 GPU 06 GPU硬件电路(4)

1.1 二维材料的基本分类与特性

材料类别

代表材料

结构对称性

能带特性

迁移率(cm²/Vs)

带隙(eV)

特殊性质

过渡金属硫族化合物(TMDs)

MoS₂, WS₂, WSe₂, MoTe₂

六方晶系(D₃h)

直接/间接带隙

10-200(单层)

1.1-2.1

强自旋轨道耦合,谷物理

石墨烯类

石墨烯,石墨炔

六方晶系(D₆h)

零带隙/狄拉克锥

10⁴-10⁵

0(可调)

超高迁移率,高透光性

黑磷(BP)

黑磷,蓝磷

正交晶系

直接带隙,各向异性

10³-10⁴

0.3-2.0

高迁移率,强面内各向异性

Xenes

硅烯,锗烯,锡烯

六方晶系

狄拉克材料

理论高

可调

拓扑绝缘体特性

h-BN

六方氮化硼

六方晶系

宽带隙绝缘体

-

~6.0

原子级平整,无悬挂键

MXenes

Ti₃C₂Tₓ, Mo₂CTₓ

六方晶系

金属/半导体

10²-10³

可调

高导电性,亲水性

1.2 能带结构理论与层数依赖

紧束缚模型哈密顿量:

对于TMDs单层:

H(k)=2Δσz+λτ2σz−1sz+at(τkxσx+kyσy)+4m0ℏ2k2(α+βσz)

其中:

-

Δ:带隙

-

λ:自旋轨道耦合强度

-

τ = ±1:谷自由度(K或K'谷)

-

s_z = ±1:自旋自由度

-

σ:赝自旋(导带/价带)

-

a:晶格常数

-

t:跳跃积分

层数依赖的能带变化:

层数

MoS₂带隙类型

带隙大小(eV)

物理机制

1L

直接

~1.9

量子限域,对称性破缺

2L

间接

~1.6

层间耦合,能带重整化

3L

间接

~1.4

体材料特性开始显现

Bulk

间接

~1.3

完全体材料特性

谷物理与自旋-谷锁定:

在TMDs中,由于空间反演对称性破缺和时间反演对称性,K和K'谷的电子具有:

-

相反的自旋极化

-

相反的贝里曲率

-

光学选择定则:σ⁺光激发K谷,σ⁻光激发K'谷

1.3 异质结能带工程

范德华异质结类型:

异质结类型

能带对齐

示例

应用

Type-I(跨立型)

一个带隙完全在另一个内

MoS₂/WS₂

发光器件,激光

Type-II(交错型)

带边错开,电荷分离

MoS₂/WSe₂, BP/MoS₂

光电探测器,太阳能电池

Type-III(破隙型)

带隙不重叠

石墨烯/h-BN/半导体

隧穿器件,负微分电阻

莫尔超晶格:

当两层二维材料以小扭转角堆叠时,形成莫尔图案,导致:

-

超晶格周期:L=a/(2sin(θ/2))

-

能带重整化:形成微能带,带宽减小

-

强关联物理:在魔角(θ≈1.1°石墨烯)处出现平带,导致超导、磁性等

2.1 玻尔兹曼输运方程

分布函数演化:

∂t∂f+v⋅∇rf+ℏq(E+v×B)⋅∇kf=(∂t∂f)coll

其中碰撞项包括各种散射机制。

线性响应电导:

在弛豫时间近似下:

σαβ=4π2q2∫d2kτ(k)vα(k)vβ(k)(−∂E∂f0)

对于各向同性抛物线能带:

σ=m∗nq2⟨τ⟩

2.2 二维系统的特殊输运现象

现象

物理机制

数学描述

实验特征

弹道输运

平均自由程>器件尺寸

L<λmfp

电导量子化,无散射

弱局域化

量子干涉,时间反演对称

Δσ(B)∝−B1/2

低温负磁阻

量子霍尔效应

朗道能级,边缘态

σxy=νe2/h

平台,整数量子化

分数量子霍尔

强关联,复合费米子

σxy=qphe2

分数量子化,石墨烯中观测

谷霍尔效应

贝里曲率,谷选择

谷极化电流

非局域测量,光学探测

自旋霍尔效应

自旋轨道耦合

自旋积累

非局域电阻,克尔旋转

2.3 散射机制与迁移率

散射机制

散射率公式

温度依赖

对迁移率影响

声学声子形变势

1/τac=ℏ3ρvs2Dac2kBTm∗

∝ T

μ∝1/T

声学声子压电

1/τpz=ℏ3ϵe2P2kBTm∗

∝ T

μ∝1/T

极性光学声子

1/τpop=2ℏe2ω0m∗(ϵ∞1−ϵ01)(n0+21∓21)

复杂

高温主导

带电杂质散射

1/τimp=8πℏ2ϵ2nimpe4kFm∗∫01(1−u2)1/2du[u+qTF/(2kF)1]2

∝ 1/n

低温主导

表面粗糙度散射

1/τsr=ℏ3m∗e4ΛΔ2(nNdep)2

与n⁻²相关

高载流子浓度

远程库仑散射

1/τremote=8πℏ2ϵ2e4kFm∗d2nremote

与d²相关

介质/界面相关

迁移率理论极限:

对于MoS₂单层,本征迁移率极限:

-

声学声子散射主导:~410 cm²/Vs

-

光学声子散射主导(300K):~130 cm²/Vs

-

实验值:1-200 cm²/Vs,受杂质散射限制

3.1 二维晶体管的基本方程

静电学:

二维系统的泊松方程:

dzd(ϵ(z)dzdϕ)=−ρ(z)

其中电荷密度ρ(z)=−ensδ(z),n_s为面电荷密度。

量子电容:

对于二维系统,量子电容为:

Cq=e2dEFdns=πℏ2e2m∗(抛物线能带)

总栅电容:Ctotal1=Cox1+Cq1

表面势与阈值电压:

Vth=ϕms−CoxQox+Qit+2ϕF

其中ϕF=q1(EF−Ei)

3.2 短沟道效应抑制机制

二维材料的天然优势:

-

超薄体厚度:t_body ≈ 0.7nm(单层MoS₂),极大抑制漏致势垒降低(DIBL)

-

无悬挂键:减少界面态,抑制短沟道效应

-

高有效质量:降低直接隧穿概率

短沟道效应度量:

-

自然长度:λ=ϵoxϵ2Dt2Dtox

-

对于单层MoS₂(ε_r≈6, t≈0.7nm),t_ox=3nm HfO₂(ε_r≈25):λ≈0.6nm

-

满足L_g > 3λ即可抑制短沟道效应,理论上L_g可缩至~2nm

3.3 弹道输运极限

弹道电流公式:

Landauer公式:

IDS=h2q∫−∞∞T(E)M(E)[fS(E)−fD(E)]dE

其中M(E)是模式数:

对于抛物线能带:M(E)=πWℏ22m∗(E−Ec)

对于狄拉克能带(石墨烯):M(E)=π2WℏvF∣E∣

弹道注入速度:

vinj=πm∗2kBT(非简并)

vinj=vF(石墨烯,简并)

4.1 接触类型与势垒

接触类型

金属-半导体组合

势垒高度(eV)

接触电阻(Ω·μm)

机制

肖特基接触

Ti/Au-MoS₂, Ni-MoS₂

0.1-0.3

1k-10k

热发射/隧穿

准欧姆接触

Sc-MoS₂, Ti-WS₂

0.05-0.15

0.5k-2k

费米能级钉扎弱

欧姆接触

石墨烯-MoS₂, NbSe₂-MoS₂

~0

0.1k-0.5k

范德华间隙,无钉扎

掺杂接触

化学/静电掺杂

可调

0.2k-1k

降低隧穿势垒宽度

相变接触

1T'-MoS₂(金属相)

0

0.05k-0.2k

金属-金属接触

费米能级钉扎:

由金属-半导体界面的间隙态引起:

ϕB=S(ϕM−χ)+(1−S)(Eg−ϕ0)

其中钉扎因子S:

-

S≈1:无钉扎(理想肖特基)

-

S≈0:强钉扎(金属诱导间隙态MIGS)

二维材料特殊钉扎机制:

-

范德华间隙:弱波函数交叠,减少MIGS

-

表面无悬挂键:减少界面态

-

金属诱导间隙态(MIGS):仍存在于金属-二维材料界面

4.2 接触电阻理论与优化

总电阻组成:

Rtotal=RC+Rch=RC+μCox(VGS−Vth)L

比接触电阻:

传输线法测量:

Rtotal=2RC+RshWL

其中RC=WRshρCcoth(dρCRsh)

接触电阻理论极限:

量子极限:RC≥2q2Mh=M12.9kΩ

M为传输模式数,对于单层MoS₂,M≈2-4

降低接触电阻策略:

策略

方法

原理

效果

金属工程

低功函数金属(Sc, Y)

降低电子势垒

R_C降至~0.5kΩ·μm

掺杂

KCl掺杂,PEI,分子

增加载流子浓度

R_C降至~0.3kΩ·μm

相变工程

激光/电流诱导1T'相

形成金属-金属接触

R_C降至~0.2kΩ·μm

边缘接触

金属与边缘键合

更强的波函数交叠

R_C降至~0.5kΩ·μm

范德华接触

半金属(石墨烯)接触

无费米能级钉扎

R_C降至~0.3kΩ·μm

缓冲层

h-BN夹层

减少金属诱导间隙态

改善稳定性

5.1 基本器件结构

结构类型

示意图

栅控效率

关键工艺

应用场景

背栅结构

二维材料/介质/Si衬底(Si为栅)

低(α≈0.1-0.3)

简单,机械剥离

基础研究,快速原型

顶栅结构

介质/二维材料/介质/底栅

中(α≈0.3-0.7)

介质沉积,金属栅

高性能,主流研究

全局栅

二维材料/介质/全局金属栅

中高

介质质量关键

高性能,低寄生

围栅/全环绕栅

介质/二维材料/介质/栅

高(α>0.8)

复杂工艺

短沟道,终极微缩

双栅结构

二维材料夹在双栅间

很高(α≈0.9)

对准,介质沉积

高驱动,对称输运

栅控效率:

α=Cox+Cq+Cit+CdepCox

其中C_it为界面态电容,C_dep为耗尽电容(二维材料中通常很小)

5.2 先进器件概念

器件概念

工作机制

优势

挑战

隧穿场效应管(TFET)

带间隧穿

亚60mV/dec摆幅,低功耗

低导通电流,工艺复杂

负电容FET(NCFET)

铁电负电容放大

陡峭摆幅,低电压

铁电材料,可靠性

自旋FET

自旋注入/探测

非易失,低功耗

自旋注入效率,温度

谷FET

谷自由度操控

谷极化,新逻辑

谷寿命,操控技术

光电FET

光生载流子

高增益,宽谱响应

响应速度,暗电流

忆阻器/突触器件

离子迁移,相变

多态,模拟计算

一致性,耐久性

5.3 短沟道器件设计

尺度极限分析:

物理效应

极限条件

单层MoS₂的极限尺寸

直接隧穿

t_ox > 1nm(约)

EOT~0.5nm(理论)

DIBL

L_g > 3λ ≈ 2nm

L_g ≈ 2nm

量子限域

t_body < 2-3nm

天然满足

弹道输运

L_g < λ_mfp ≈ 100nm

可发挥弹道优势

围栅结构设计:

圆柱坐标泊松方程:

r1drd(rdrdϕ)=−ϵρ(r)

对于全环绕栅,归一化长度:

λ=2ϵoxϵ2Dt2DRln(1+tox/R)

其中R为沟道半径

6.1 完整工艺流程

1. 衬底准备

- Si/SiO₂(90nm)晶片清洗

- 或柔性衬底(聚酰亚胺,PET)预处理

2. 二维材料制备

a. 机械剥离(Scotch胶带法)

- 块体晶体粘在胶带上

- 反复剥离至薄层

- 转移到目标衬底

- 光学/AFM识别单层

b. 化学气相沉积(CVD)生长

- 前驱体:MoO₃ + S粉(MoS₂)

- 温度:700-850°C

- 气氛:Ar/H₂混合气体

- 时间:5-30分钟

- 单晶尺寸:可达毫米级

c. 金属有机化学气相沉积(MOCVD)

- 前驱体:Mo(CO)₆ + (C₂H₅)₂S

- 温度:400-600°C

- 优势:低温,大面积,均匀

d. 分子束外延(MBE)

- 超高真空(~10⁻¹⁰ Torr)

- 精确控制厚度,掺杂

- 高质量,但速度慢

3. 图案化

a. 电子束光刻(EBL)

- 旋涂PMMA(100-200nm)

- 电子束曝光

- 显影(MIBK:IPA = 1:3)

- 分辨率:~10nm

b. 原子层刻蚀(ALE)

- 自限制表面反应

- 各向异性,原子级精度

- 对二维材料损伤小

c. 选择性刻蚀

- 反应离子刻蚀(RIE):CF₄/O₂等离子体

- 湿法刻蚀:基于光刻胶掩膜

4. 介质层沉积

a. 原子层沉积(ALD)

- 前驱体:HfCl₄ + H₂O(HfO₂)

- 温度:150-300°C

- 生长速率:~0.1nm/循环

- 均匀性:<1%变化

b. 范德华介质集成

- 机械剥离h-BN

- 干法/湿法转移

- 无悬挂键,清洁界面

5. 电极制备

a. 金属沉积

- 电子束蒸发:Ti/Au(5/50nm),Cr/Au(5/50nm)

- 溅射:更均匀,但可能损伤

b. 退火处理

- 快速热退火:200-400°C,1-5分钟

- 改善接触,降低R_C

c. 范德华电极

- 石墨烯电极:CVD生长,转移

- 半金属电极:NbSe₂,TaS₂

6. 栅堆叠形成

a. 顶栅结构

- ALD介质层(3-10nm)

- 电子束蒸发栅金属(Ti/Au)

- 剥离形成栅电极

b. 全局栅结构

- 整面介质沉积

- 整面金属沉积

- 光刻+刻蚀定义栅

7. 钝化与封装

a. ALD钝化层

- Al₂O₃(10-20nm)保护

- 防止环境退化

b. h-BN封装

- 上下h-BN夹层

- 最佳保护,保持本征性能

c. 柔性封装(柔性器件)

- PDMS,聚酰亚胺涂层

6.2 范德华异质结制造

干法转移工艺:

1. 制备支撑层

- 旋涂PMMA(200-300nm)在Si/SiO₂上

- 烘烤:180°C,2分钟

2. 分离目标材料

- 将带二维材料的衬底浸入HF或KOH溶液

- 二维材料+PMMA浮起

3. 清洗与转移

- DI水清洗3次

- 用目标衬底捞起

- 干燥:室温或60°C加热

4. 去除PMMA

- 丙酮浸泡去除PMMA

- 异丙醇清洗

- 氮气吹干

5. 退火处理

- 真空退火:200-300°C,2小时

- 减少界面气泡,改善接触

湿法转移工艺(更常用):

1. 旋涂PMMA在生长衬底

2. 刻蚀牺牲层(如Cu刻蚀剂刻蚀铜箔)

3. 目标衬底捞起材料/PMMA薄膜

4. 丙酮去除PMMA

5. 异丙醇清洗,氮气吹干

6.3 关键工艺参数优化

工艺步骤

关键参数

优化值/范围

对器件性能影响

CVD生长

温度,前驱体比例,压力

MoS₂: 800°C, Mo:S≈1:100, 1atm

结晶质量,尺寸,层数均匀性

ALD介质

前驱体,温度,循环数

HfO₂: 200°C, TDMAH+H₂O, 20-40循环

界面态,漏电,栅控能力

金属接触

金属,厚度,退火条件

Sc(20nm)/Au(50nm), 300°C 2min N₂

接触电阻,肖特基势垒

光刻

剂量,显影时间,对准精度

EBL: 剂量300μC/cm², 显影60s

分辨率,边缘粗糙度,套刻误差

刻蚀

气体,功率,时间

RIE: CF₄(30sccm), 50W, 30s

各向异性,损伤,选择比

转移

温度,时间,气氛

真空退火: 200°C 2h, 10⁻⁶ Torr

界面清洁度,气泡,掺杂

7.1 基本逻辑电路

电路单元

器件需求

实现方式

性能指标

反相器

1个nFET + 1个pFET或电阻负载

互补型(CMOS)或伪nMOS

增益>10,噪声容限>VDD/4

与非门(NAND)

2个nFET串联 + 2个pFET并联

标准CMOS逻辑

延时~ps,功耗~nW

或非门(NOR)

2个nFET并联 + 2个pFET串联

标准CMOS逻辑

面积,速度对称性

传输门

nFET和pFET并联

互补开关

导通电阻低,关断漏电小

SRAM单元

6T(4T+2负载)或4T(负载集成)

交叉耦合反相器

保持静态噪声容限,读写稳定性

电压传输特性(VTC):

Vout=f(Vin)

噪声容限:NML=VIL−VOL,NMH=VOH−VIH

延时模型:

τ=IonCLVDD≈LWμCox(VDD−Vth)2CLVDD

7.2 数字电路性能

国际器件与系统路线图(IRDS)目标:

年份

节点(nm)

栅长(nm)

工作电压(V)

导通电流(μA/μm)

亚阈值摆幅(mV/dec)

延时(ps)

2025

5

12

0.5-0.6

900-1100

65-70

0.3-0.5

2030

3

8

0.4-0.5

700-900

60-65

0.2-0.4

2035

2

5

0.3-0.4

500-700

55-60

0.1-0.3

2040

1.5

3

0.2-0.3

300-500

50-55

0.05-0.2

二维材料优势:

-

更小的自然长度,可缩放到~2nm栅长

-

更高的迁移率(理论>1000cm²/Vs)

-

更薄的体厚度,更好栅控

-

潜在的弹道输运,更高速度

7.3 模拟与射频电路

关键射频参数:

-

截止频率:fT=2π(Cgs+Cgd)gm

-

最大振荡频率:fmax=2Rg(gds+2πfTCgd)fT

-

最小噪声系数:Fmin=1+2πfTgmRg+Rs

二维材料RF性能:

材料

f_T(实测)

f_T(理论)

f_max(实测)

增益(实测)

石墨烯

300 GHz

>1 THz

200 GHz

10-20 dB@10GHz

MoS₂

50 GHz

数百GHz

30 GHz

5-10 dB@10GHz

黑磷

100 GHz

数百GHz

80 GHz

8-15 dB@10GHz

InSe

80 GHz

数百GHz

60 GHz

6-12 dB@10GHz

7.4 三维异质集成

单片三维集成:

-

逐层生长/转移二维材料

-

层间介质沉积(ALD Al₂O₃, h-BN)

-

层间互连(通过孔刻蚀,金属填充)

-

优点:高密度,异质功能,低寄生

异质三维集成:

-

二维材料与硅/III-V/碳纳米管集成

-

混合键合或转移集成

-

优点:功能多样化,性能优化

热管理挑战:

-

二维材料面内热导率高(石墨烯~2000W/mK,MoS₂~50W/mK)

-

面外热导率低(石墨烯~10W/mK,h-BN~5W/mK)

-

需要热通路设计,热界面材料

8.1 电学表征

测试类型

测量参数

仪器

提取信息

直流I-V

I_DS-V_DS, I_DS-V_GS, I_G-V_GS

半导体参数分析仪

转移/输出特性,亚阈值摆幅,DIBL,开态电流

CV测量

C-V曲线(1kHz-1MHz)

LCR表,CV分析仪

氧化层厚度,界面态密度,平带电压

脉冲I-V

短脉冲(纳秒-微秒)I-V

脉冲发生器,示波器

自热效应,陷阱效应,BTI

低频噪声

1/f噪声谱密度

低噪声放大器,频谱分析仪

缺陷密度,界面质量,迁移率涨落

RF测量

S参数(0.1-110GHz)

矢量网络分析仪

f_T, f_max, 增益,稳定性,噪声

变温测量

I-V(-196°C至200°C)

低温探针台,热台

散射机制,激活能,陷阱能级

可靠性测试

NBTI/PBTI, TDDB, HCI

可靠性测试系统

寿命,退化机制,加速因子

8.2 材料与界面表征

技术

原理

信息

二维材料应用

拉曼光谱

声子模频率,强度,线宽

层数,应变,掺杂,缺陷

层数识别(E₂g, A₁g模),掺杂(G峰位移)

光致发光(PL)

激子发光强度,能量

带隙,层数,缺陷,掺杂

单层(强PL),多层(弱PL)

原子力显微镜(AFM)

针尖-样品力

形貌,厚度,表面电势

厚度测量(单层~0.7nm),表面形貌

扫描隧道显微镜(STM)

隧道电流

原子结构,缺陷,电子态

原子分辨率成像,缺陷观察

透射电镜(TEM)

电子透射,衍射

原子结构,晶格,缺陷

晶格成像,缺陷分析,层数

X射线光电子谱(XPS)

光电子能谱

元素,化学态,掺杂

元素组成,氧化态,掺杂浓度

角分辨光电子谱(ARPES)

光电子能量-动量

能带结构,费米面

能带测量,狄拉克锥观测

二次谐波产生(SHG)

非线性光学效应

晶格对称性,层数,堆叠

奇数层检测,堆叠角度

9.1 材料级挑战

挑战

具体问题

解决方案

进展

大面积均匀性

CVD生长不均匀,晶界多

单晶生长,晶圆级外延,MOCVD

4英寸晶圆演示(MoS₂)

层数控制

层数不均匀,多晶

自限制生长,选择性刻蚀

单层均匀性>90%

缺陷控制

空位,晶界,掺杂

优化生长条件,后处理

室温迁移率>100cm²/Vs

掺杂控制

可控n/p型掺杂

表面转移掺杂,离子液体,置换掺杂

可控阈值电压调节

空气稳定性

氧化,掺杂变化

h-BN封装,AL₂O₃钝化,合金化

数月稳定性已实现

接触电阻

费米能级钉扎,高电阻

相变接触,范德华接触,掺杂

R_C<0.5kΩ·μm

热稳定性

高温退化,相变

高热稳定性材料(WSe₂, MoTe₂)

可承受400-500°C

9.2 工艺集成挑战

挑战

具体问题

解决方案

进展

转移技术

污染,破损,皱褶

干法转移,卷对卷,直接生长

洁净界面,高成品率

图案化

边缘粗糙,损伤

原子层刻蚀,选择性刻蚀

原子级平滑边缘

介质集成

界面态,陷阱

范德华介质(h-BN),原位ALD

D_it<10¹¹ eV⁻¹cm⁻²

金属化

反应,扩散,高电阻

低温沉积,扩散阻挡层,范德华接触

比接触电阻<10⁻⁸ Ω·cm²

对准精度

多层对准误差

自对准工艺,先进光刻

套刻误差<5nm

热预算

高温工艺限制

低温工艺(<400°C),激光退火

柔性衬底兼容

9.3 器件与电路挑战

挑战

具体问题

解决方案

进展

n/p型对称性

多数材料单极型

接触工程,掺杂,双材料集成

CMOS反相器演示

短沟道效应

亚5nm尺度控制

超薄体,围栅结构,高k介质

1nm物理栅长演示

自热效应

低热导率,热瓶颈

热管理,散热设计,悬浮结构

热导率测量与优化

统计变化

材料,界面,接触变化

统计设计,冗余,工艺控制

统计模型建立

可靠性

BTI,HCI,TDDB

界面工程,介质优化,设计余量

初步可靠性研究

频率响应

寄生电容电阻

自对准,空气桥,低k介质

f_T>100GHz演示

10.1 数字集成电路

应用领域

优势

技术挑战

发展状态

超大规模集成电路

微缩至2nm以下,低功耗

晶圆级集成,成品率,可靠性

研究阶段,原型演示

低功耗物联网

亚阈值摆幅小,低电压工作

工艺变化,良率

实验室演示

柔性电子

柔韧性,透明性

柔性衬底集成,可靠性

柔性CPU演示

三维集成电路

单片三维集成,高密度

热管理,工艺复杂性

概念验证

存内计算

存储器与逻辑集成

材料选择,电路设计

研究阶段

10.2 模拟与射频电路

应用领域

优势

技术挑战

发展状态

毫米波/太赫兹

高f_T/f_max,低噪声

寄生参数,阻抗匹配

高频器件演示

低噪声放大器

高迁移率,低1/f噪声

噪声匹配,线性度

研究阶段

射频开关

高线性度,低插入损耗

功率处理,隔离度

初步演示

混频器

高转换增益,低功耗

线性度,端口隔离

实验室演示

压控振荡器

高频,低相位噪声

频率稳定性,调谐范围

研究阶段

10.3 传感器与探测器

传感器类型

传感机制

灵敏度

应用领域

光电探测器

光生载流子,光伏效应

高增益(10³-10⁵),宽谱

成像,通信,夜视

气体传感器

电荷转移,电导变化

ppb级检测限

环境监测,安全

生物传感器

生物分子吸附,电导变化

单分子检测(理论)

医疗诊断,生物检测

应变传感器

压阻效应,能带变化

高规整因子(>100)

可穿戴,人机接口

湿度传感器

水分子吸附,介电变化

宽范围(0-100%RH)

环境监测,工业控制

10.4 新兴应用

应用领域

物理机制

独特优势

挑战

自旋电子学

自旋注入,输运,探测

长自旋弛豫时间,谷物理

自旋注入效率,温度

谷电子学

谷自由度操控

低功耗,新逻辑

谷寿命,谷极化

神经形态计算

忆阻,突触可塑性

多态,模拟计算

一致性,耐久性

量子计算

量子点,自旋量子比特

长相干时间(理论)

控制,读取,扩展

柔性/透明电子

机械柔韧,光学透明

可弯曲,可拉伸,透明

稳定性,集成密度

能量收集

热电,压电,光伏

自供电,多功能

效率,集成

11.1 近期目标(2023-2028)

目标

技术指标

关键突破

晶圆级材料生长

4-8英寸,单层均匀性>95%

MOCVD,MBE大面积生长

高性能晶体管

开态电流>1mA/μm,亚阈值摆幅<70mV/dec

接触工程,高k介质

基本电路演示

1000级以上门电路,>1GHz频率

低损伤工艺,设计方法学

n/p型对称

对称CMOS,阈值电压可调

掺杂技术,双材料集成

柔性电子

弯曲半径<1mm,>1000次弯曲

柔性衬底集成,封装

11.2 中期目标(2028-2035)

目标

技术指标

关键突破

先进节点器件

栅长5nm,性能超越硅

围栅结构,弹道输运

三维异质集成

3层以上堆叠,混合集成

范德华集成,热管理

系统级演示

8位以上处理器,存储器阵列

设计自动化,测试技术

新功能器件

自旋FET,谷器件,量子器件

新物理效应,操控技术

产业化试点

特定应用产品(传感器,RF)

成本控制,可靠性认证

11.3 长期愿景(2035-2050)

愿景

技术特征

潜在应用

后硅时代主力

2nm以下节点,三维单片集成

高性能计算,人工智能

异构集成平台

二维材料+硅+III-V+光子

多功能系统,智能传感

量子技术平台

量子计算,量子通信

量子计算机,安全通信

生物集成系统

生物-电子接口,可植入

脑机接口,健康监测

绿色电子

可降解,低能耗,可持续

环境友好电子,物联网

12.1 核心优势

-

原子级厚度:天然超薄体,优异静电控制,可微缩至2nm以下

-

无悬挂键表面:减少界面态,高迁移率潜力

-

可调能带结构:层数,应变,堆叠调控能带

-

机械柔韧性:适用于柔性,可穿戴电子

-

光学透明性:透明电子,光电集成

-

丰富物理特性:自旋,谷,拓扑等新自由度

-

范德华异质集成:无需晶格匹配,自由堆叠

12.2 主要挑战

-

材料合成:晶圆级单晶,层数控制,缺陷控制

-

接触电阻:费米能级钉扎,高接触电阻

-

掺杂技术:可控,稳定,均匀的n/p型掺杂

-

工艺集成:低温工艺,高k介质集成,金属化

-

可靠性:BTI,HCI,自热,环境稳定性

-

电路设计:统计变化,设计工具,设计方法学

-

制造成本:与传统硅工艺的竞争力

12.3 当前状态与展望

二维材料晶体管经过十多年发展,已从基础研究进入技术开发阶段:

-

材料合成:4英寸晶圆级生长已实现,质量逐步提升

-

单器件性能:开态电流>1mA/μm,亚阈值摆幅接近理论极限

-

基本电路:反相器,逻辑门,简单电路已演示

-

特殊应用:柔性显示,传感器等已接近实用化

未来发展方向:

-

材料工程:高质量晶圆级生长,新材料探索(磁性,拓扑)

-

接触工程:超低电阻欧姆接触,可调控肖特基势垒

-

器件架构:围栅,负电容,隧穿等新结构

-

异质集成:二维材料与硅,III-V,光子集成

-

新功能器件:自旋,谷,量子,神经形态器件

-

系统集成:三维集成,存算一体,感算一体

二维材料晶体管作为后摩尔时代的重要技术路径,有望在特定应用领域(如柔性电子,传感,射频)率先实现商业化,并最终在高级节点集成电路中发挥关键作用。其发展需要材料,器件,电路,系统等多层面的协同创新,以及与现有硅基技术的深度融合。

1.1 铁电材料的基本特性

特性

描述

数学表达

物理意义

自发极化

无外场时的电极化

Ps

铁电性的根本特征

电滞回线

极化随电场的变化

P(E)回线

非线性和记忆效应

矫顽电场

极化反转所需场强

Ec

铁电开关的难易程度

剩余极化

外场为零时的极化

Pr

存储的信息状态

相对介电常数

介电响应

ϵr=dEdD

可正可负(负电容)

居里温度

铁电-顺电转变温度

TC

工作温度上限

电滞回线特征方程:

对于经典铁电体,极化P与电场E的关系为:

E=αP+βP3+γP5

其中α<0(铁电相),β>0,γ决定回线形状。

1.2 负电容的物理起源

热力学定义:

电容 C=dVdQ,当dEdP<0时,介电常数ϵr<0,对应负电容。

Landau-Devonshire理论:

铁电自由能密度展开:

U(P)=αP2+βP4+γP6−EP

其中α=α0(T−TC),T为温度,T_C为居里温度。

负电容条件:

dP2d2U=2α+12βP2<0

在极化反转的中间状态(P接近0),α<0导致二阶导为负,系统处于不稳定态,与外部电容耦合时能稳定在负斜率区。

稳态条件:

铁电层与介质层串联系统的总能量最小化:

dPdUFE=EFE=EDE=ϵ0ϵDEP

通过求解此方程,可得到稳定的负电容工作点。

1.3 负电容的稳定性条件

稳定判据:

铁电电容(C_FE)与外部电容(C_ext)串联,系统稳定的条件为:

dPdEFE>dPdEext

或等价地:

CFE−1+Cext−1>0

其中CFE=dEFEdP<0。

稳定工作区域:

在电滞回线的负斜率区,当满足:

∣CFE∣<Cext

时,系统可稳定工作在负电容态(无回滞)。

2.1 基本结构

结构类型

示意图

铁电层位置

栅堆叠顺序

特点

金属-铁电-金属-绝缘体-半导体 (MFMIS)

栅极-铁电-金属-介质-半导体

栅极与金属层之间

Gate/FE/M/DE/S

电压放大,但需金属层

金属-铁电-绝缘体-半导体 (MFIS)

栅极-铁电-介质-半导体

栅极与介质之间

Gate/FE/DE/S

直接耦合,简单

负电容FinFET (NC-FinFET)

铁电层包裹鳍

栅堆叠顶部

Gate/FE/DE/Fin

三维栅控,高密度

负电容纳米片 (NC-Nanosheet)

铁电层环绕纳米片

全环绕

Gate/FE/DE/Sheet

最强栅控,短沟道优

负电容隧道FET (NC-TFET)

铁电+隧穿结构

栅堆叠

Gate/FE/DE/Source-Channel

超低功耗,陡峭开关

栅堆叠电容模型:

总栅电容:

CG1=CFE1+CDE1+Cinv1

其中Cinv为反型层电容。

内部电压放大:

铁电层的负电容效应放大栅压:

Vint=VG×∣CFE∣−CDE∣CFE∣

当∣CFE∣接近CDE时,放大因子最大。

2.2 亚阈值摆幅理论

传统MOSFET极限:

玻尔兹曼 tyranny限制:

S=d(logID)dVG=ln(10)qkT(1+CoxCdep+Cit)≥60mV/dec

负电容突破:

负电容提供内部电压放大,有效降低摆幅:

SNC=1−∣CFE∣CDES0

其中S0为无铁电时的摆幅。

极限情况:

当∣CFE∣=CDE时,理论上S→0(实际受量子电容限制)。

考虑量子电容:

实际极限:

Smin=ln(10)qkTCQ+CeffCQ

其中Ceff为铁电放大后的有效电容。

2.3 工作模式

模式

铁电状态

电容符号

电压放大

回滞

应用

无回滞模式

稳定在负斜率区

C_FE < 0

是

无

低功耗逻辑

回滞模式

极化翻转

正负变化

是

有

存储器,神经形态

部分翻转模式

部分极化翻转

可正可负

是

可能

多态存储

不稳定性模式

不稳定振荡

剧烈变化

振荡

振荡

避免

稳定工作窗口:

通过设计铁电层厚度和介质层厚度,控制电容比:

tDEtFE=ϵDEϵFE×∣CFE∣CDE

通常需要tFE/tDE≈0.1−0.5以获得稳定负电容。

3.1 主要铁电材料

材料

晶体结构

剩余极化(μC/cm²)

矫顽场(MV/cm)

居里温度(°C)

兼容性

Pb(Zr,Ti)O₃ (PZT)

钙钛矿

10-60

0.05-0.1

200-400

差(含Pb)

BaTiO₃ (BTO)

钙钛矿

5-20

0.01-0.05

120

中等

SrBi₂Ta₂O₉ (SBT)

层状钙钛矿

5-15

0.03-0.06

300

较好

HfO₂基(HZO, HfZrO₃)

正交/单斜

10-40

1-2

400-500

优秀

AlScN

纤锌矿

100-150

3-5

>1000

优秀

PVDF-TrFE

聚合物

5-10

0.5-1

70-100

柔性

CuInP₂S₆

二维层状

3-10

0.1-0.3

40-60

二维集成

HfO₂基铁电的优势:

-

CMOS兼容:与现有工艺完全兼容

-

高矫顽场:适合薄膜器件(~1-2 MV/cm)

-

可微缩:厚度可降至~5 nm

-

无铅:环境友好

HZO铁电特性:

-

Zr含量:~50%时铁电性最强

-

厚度:>5 nm才能保持铁电性

-

退火:快速热退火(400-600°C)诱导正交相

-

应力:影响铁电性,需优化工艺

3.2 铁电相变理论

HfO₂的相结构:

相

对称性

介电常数

稳定性

铁电性

单斜(m)

P2₁/c

~20

最稳定

无

四方(t)

P4₂/nmc

~30-40

高温相

无

立方(c)

Fm-3m

~30

高温相

无

正交(o)

Pca2₁

~30-40

亚稳

有

铁电性起源:

HfO₂中正交相(Pca2₁)的非中心对称结构导致自发极化,沿[001]方向极化强度可达~10-40 μC/cm²。

尺寸效应:

薄膜厚度对铁电性的影响:

-

10 nm:铁电性稳定

-

5-10 nm:铁电性存在,但可能减弱

-

<5 nm:铁电性通常消失

掺杂效应:

掺杂元素可稳定正交相:

-

Si, Al, Y, La, Gd:掺杂浓度~2-8%

-

Zr:与Hf形成固溶体HZO

3.3 铁电薄膜制备

制备方法

原理

优点

缺点

适用材料

原子层沉积(ALD)

自限制表面反应

均匀性佳,共形性

速度慢,掺杂控制

HZO, HfO₂基

磁控溅射

等离子体溅射

速度快,质量好

均匀性一般

PZT, BTO

脉冲激光沉积(PLD)

激光烧蚀

化学计量控制好

面积小,成本高

复杂氧化物

溶胶-凝胶法

溶液旋涂退火

低成本,简单

针孔,均匀性差

PZT, SBT

分子束外延(MBE)

原子层外延

质量极佳,控制精

极慢,成本极高

研究用途

ALD工艺示例(HZO):

前驱体:TDMAH + TEMAZr + H₂O/O₃

温度:250-300°C

循环比:Hf:Zr ≈ 1:1

厚度:5-20 nm

后处理:快速热退火,400-600°C,30-60s,N₂气氛

结晶:形成正交铁电相

4.1 Landau-Khalatnikov方程

动力学方程:

描述极化随时间演化:

ρdtdP+∂P∂U=E

其中ρ是阻尼系数,U(P)是Landau自由能。

稳态解:

忽略时间项:

2αP+4βP3+6γP5=E

小信号响应:

对稳态解线性化,得到微分电容:

CFE−1=dPdE=2α+12βP2+30γP4

4.2 负电容晶体管模型

表面势放大:

铁电层放大栅压对表面势的控制:

ψs=CFE−CDECFEVG′

其中VG′=VG−VFB,V_FB为平带电压。

电流-电压特性:

考虑负电容效应后,传统MOSFET方程修正为:

亚阈值区:

ID=I0exp(neffkTq(VG−VT))

其中有效斜率因子:

neff=1+CeffCdep+Cit

而Ceff=(CDE1−∣CFE∣1)−1>CDE

强反型区:

ID=LWμCeff[(VG−VT)VD−21VD2](线性区)

ID=2LWμCeff(VG−VT)2(饱和区)

4.3 小信号模型

等效电路:

G

│

├─C_FE─┐

│ │

└─R_FE─┤

│ │

└─C_DE─┤

│ │

│ g_mV_gs

│ │

└─C_inv─┤

│ │

S D

其中:

-

C_FE:铁电电容(可负)

-

R_FE:铁电损耗电阻

-

C_DE:介质层电容

-

C_inv:反型层电容

跨导增强:

由于内部电压放大,有效跨导增加:

gm,eff=gm×∣CFE∣−CDE∣CFE∣

截止频率:

fT=2π(Cgs+Cgd)gm,eff

由于C_gs包含铁电电容,需重新计算。

5.1 完整工艺流程(以HZO NCFET为例)

1. 衬底准备

a. 硅晶片清洗(RCA标准清洗)

b. 离子注入形成阱区(如有需要)

c. 浅槽隔离(STI)或LOCOS隔离

2. 有源区形成

a. 光刻定义有源区

b. 干法刻蚀硅

c. 栅氧化层生长(如有需要,1-2 nm SiO₂界面层)

3. 介质层沉积

a. ALD沉积高k介质(HfO₂, Al₂O₃等)

- 厚度:1-3 nm EOT

- 温度:250-300°C

- 前驱体:TDMAH, TMA, TEMAHf等

4. 铁电层沉积

a. ALD沉积HZO

- 循环比:Hf:Zr ≈ 1:1

- 厚度:5-15 nm

- 温度:250-300°C

b. 铁电层图案化

- 光刻定义铁电层图形

- 干法刻蚀(Cl₂/BCl₃/Ar等离子体)

- 光刻胶去除

5. 铁电层结晶化

a. 快速热退火(RTA)

- 温度:400-600°C

- 时间:30-60秒

- 气氛:N₂或O₂

b. 退火优化

- 温度梯度控制

- 应力工程(盖帽层)

6. 栅电极形成

a. 栅金属沉积

- TiN(10-20 nm)作为功函数层

- W或Al(50-100 nm)作为填充

- 方法:PVD或ALD

b. 栅电极图案化

- 光刻定义栅图形

- 干法刻蚀

- 侧墙形成(如有需要)

7. 源漏工程

a. 延伸区注入

- 低能量离子注入

- 种类:As(nFET),B(pFET)

b. 侧墙形成

- 沉积SiO₂/SiN

- 各向异性刻蚀

c. 源漏注入

- 高剂量离子注入

d. 快速热退火

- 激活掺杂,修复损伤

8. 接触与金属化

a. 硅化物形成(NiSi, CoSi₂)

b. 接触孔刻蚀

c. W栓塞填充

d. 铜互连(双大马士革工艺)

9. 后端工艺

a. 层间介质沉积

b. 钝化层沉积

c. 焊盘开口

5.2 关键工艺优化

工艺步骤

关键参数

优化目标

挑战与解决方案

铁电层沉积

厚度,组分,均匀性

稳定负电容,无回滞

厚度控制(~10nm),Hf:Zr比例(~1:1)

结晶退火

温度,时间,气氛

正交相形成,低缺陷

快速热退火(~500°C),避免过度晶化

界面控制

界面层厚度,质量

低界面态,高迁移率

SiO₂界面层<1nm,氮化处理

栅堆叠集成

功函数,热预算

合适V_T,低漏电

TiN功函数层,低温工艺<600°C

图案化

刻蚀选择性,损伤

侧壁垂直,无铁电损伤

高选择比刻蚀,损伤修复退火

可靠性

BTI,TDDB,疲劳

长寿命,稳定铁电性

界面优化,操作条件控制

5.3 先进集成方案

集成方案

结构特点

优势

挑战

后道集成

铁电层在M1后集成

低温工艺,兼容性好

寄生电容,性能限制

中间道集成

铁电层在栅与接触之间

平衡性能与兼容性

热预算控制

前道集成

铁电层在栅介质中

高性能,标准工艺

高温工艺挑战

单片三维集成

多层NCFET堆叠

高密度,异质集成

散热,工艺复杂性

柔性集成

铁电聚合物在柔性衬底

柔性,透明,低成本

性能,稳定性

6.1 直流特性

参数

传统MOSFET

负电容FET

改善因子

物理机制

亚阈值摆幅(SS)

≥60 mV/dec

可<60 mV/dec

可达2-3倍

内部电压放大

导通电流(I_on)

由迁移率等决定

相同V_G下更高

1.2-2倍

有效栅压增加

阈值电压(V_T)

由功函数等决定

可更低

可调

铁电极化影响

漏致势垒降低(DIBL)

短沟道严重

可改善

改善~30%

栅控增强

开关比(I_on/I_off)

10⁴-10⁷

可更高

改善

SS改善

跨导(g_m)

常规值

更高

1.5-3倍

有效栅压放大

亚阈值摆幅测量:

从转移特性提取:

SS=d(log10ID)dVG=qkTln(10)(1+CeffCdep+Cit)

NCFET中Ceff>Cox,故SS降低。

回滞窗口:

铁电迟滞导致的V_T偏移:

ΔVT=CDE2Pr

其中P_r为剩余极化。

6.2 频率特性

小信号等效电路参数:

参数

表达式

NCFET特点

影响

输入电容C_gg

C_gs + C_gd

包含铁电电容,可能更大

速度可能降低

跨导g_m

∂I_D/∂V_GS

因放大效应而增加

f_T可能增加

栅电阻R_g

由栅材料决定

铁电层可能增加电阻

f_max可能降低

输出电阻r_o

∂V_DS/∂I_D

与常规FET类似

增益类似

截止频率f_T:

fT=2π(Cgs+Cgd)gm

由于g_m增加可能超过C_gg增加,f_T可能提高。

最大振荡频率f_max:

fmax=2Rg(gds+2πfTCgd)fT

需优化R_g和C_gd。

6.3 瞬态特性

开关延迟:

由于负电容效应,开关速度可能提高:

τ=IonCGVDD≈Ion(CDE−∣CFE∣)VDD

有效电容降低,延迟减小。

极化翻转时间:

铁电极化响应时间:

τFE=ρCFE≈0.1−1 ns

限制了最高工作频率。

7.1 数字电路设计

反相器特性:

NCFET反相器的电压传输特性更陡峭,噪声容限提高:

NM=2VOH−VOL(理想情况下)

实际噪声容限提高~20-50%。

功耗分析:

总功耗 Ptotal=Pdynamic+Pstatic+Pshort−circuit

动态功耗:

Pdynamic=αCeffVDD2f

由于C_eff可能降低,动态功耗降低。

静态功耗:

Pstatic=IoffVDD

由于SS降低,相同I_on下I_off更低,静态功耗降低。

短沟道功耗:

由于开关更陡峭,短路功耗可能降低。

性能-功耗权衡:

工作点

V_DD (V)

速度

功耗

NCFET优势

高性能

0.7-0.9

高

中

速度更高

低功耗

0.3-0.5

中

低

功耗更低

超低功耗

0.2-0.3

低

极低

仍能工作

7.2 存储器应用

铁电存储器(FeRAM):

利用铁电回滞存储数据:

-

写入:施加脉冲极化铁电层

-

读取:检测极化状态

-

优势:非易失,速度快,耐久性好

负电容存储器:

利用负电容状态存储多值信息:

-

多个稳定负电容态对应多bit存储

-

读取:通过电流或电容测量

-

优势:密度高,功耗低

1T存储器单元:

单个NCFET可存储信息,无需额外电容:

-

利用回滞窗口存储

-

简单,高密度

-

挑战:读出放大,干扰

7.3 模拟与射频电路

放大器设计:

由于g_m提高,增益提高:

Av=−gm(ro∥RD)

可设计更高增益的放大器。

低噪声放大器(LNA):

由于g_m提高,噪声系数可能改善:

Fmin=1+2πfCgsgmRg+Rs

振荡器:

由于g_m提高,起振条件更容易满足:

gm≥Rp1+Rn1

模数转换器(ADC):

更陡的转移特性提高精度,降低比较器失调。

7.4 神经形态计算

突触器件:

利用铁电多态实现权值存储:

-

极化程度对应权值大小

-

可模拟实现

-

非易失,低功耗

神经元器件:

利用负电容实现更生物真实的激活函数:

-

陡峭的开关特性类似神经元

-

可实现脉冲神经元

全铁电神经网络:

利用NCFET构建全铁电神经网络:

-

高能效

-

在线学习能力

-

非易失存储

8.1 铁电退化机制

机制

描述

影响

缓解策略

疲劳

极化翻转次数增加导致P_r下降

存储器耐久性限制

优化电极,界面工程

印记

偏置温度应力下V_T偏移

数据保留问题

平衡掺杂,优化工艺

保持

时间依赖性极化衰减

数据丢失

优化矫顽场,封装

击穿

电场过强导致介质击穿

灾难性失效

厚度优化,电场限制

疲劳特性:

极化翻转N次后剩余极化衰减:

Pr(N)=Pr0exp(−N/N0)

N_0为特征翻转次数,HZO通常>10¹⁰次。

印记模型:

偏置温度应力下的V_T漂移:

ΔVT=Alog(t)+Bexp(−Ea/kT)

8.2 负电容稳定性

回滞问题:

铁电迟滞导致回滞窗口,对逻辑电路不利:

ΔVhys=ϵ0ϵFE2EctFE(1−∣CFE∣CDE)

减小方法:降低铁电厚度,优化电容匹配。

温度稳定性:

负电容效应与温度相关:

-

居里温度限制工作温度范围

-

极化强度随温度变化

-

需要宽温度范围铁电材料

频率依赖性:

负电容效应频率范围有限:

-

低频:稳态负电容

-

高频:铁电响应跟不上,负电容消失

-

典型范围:DC~GHz

8.3 与CMOS工艺的兼容性

兼容性问题

描述

解决方案

热预算

铁电结晶需高温(~500°C)

后道集成,低温结晶

污染

金属扩散,污染前端

扩散阻挡层,优化集成

应力

铁电薄膜产生应力

应力工程,应变补偿

界面

铁电/介质界面质量

界面层优化,表面处理

可靠性

与传统CMOS可靠性差异

协同优化,设计余量

9.1 铁电特性测试

测试方法

测量参数

原理

设备

P-E电滞回线

P_r, E_c, 回滞

双波形法,Sawyer-Tower电路

铁电分析仪

C-V回滞

电容回滞,记忆窗口

高频C-V扫描

阻抗分析仪,CV仪

脉冲测试

极化翻转速度,疲劳

脉冲写入,脉冲读取

脉冲发生器,示波器

压电响应力显微镜(PFM)

局部铁电性,极化方向

压电效应,AFM技术

原子力显微镜

X射线衍射(XRD)

晶体结构,相组成

布拉格衍射

X射线衍射仪

透射电镜(TEM)

微观结构,界面

电子衍射,高分辨成像

透射电镜

P-V测量设置:

Sawyer-Tower电路测量电荷Q,计算极化P=Q/A:

-

三角波或双极脉冲激励

-

积分电路测量电荷

-

补偿漏电和线性电容

C-V回滞分析:

从高频C-V曲线提取:

-

记忆窗口:ΔV = 2E_c t_FE

-

负电容区域:C > C_ox的区域

-

界面态密度:从频散提取

9.2 器件特性测试

测试类型

测量

提取参数

注意事项

直流I-V

I_D-V_G, I_D-V_D

SS, I_on/I_off, V_T, DIBL

慢扫描,避免自热

回滞测试

双向V_G扫描

回滞窗口,记忆窗口

扫描速度,范围

脉冲I-V

短脉冲测量

自热效应,铁电响应时间

脉冲宽度,占空比

电容-电压

C-V曲线

C_ox, C_FE, 界面态

频率,幅度

栅极漏电

I_G-V_G

铁电漏电,击穿场强

应力时间,软击穿

可靠性测试

BTI, TDDB, 疲劳

寿命,退化机制

应力条件,监测

亚阈值摆幅提取:

从转移曲线(对数坐标)线性区拟合:

SS=Δ(log10ID)ΔVG

需验证无回滞影响。

增益提取:

从反相器电压传输特性:

Gain=dVindVoutmax

NCFET反相器增益可>100。

9.3 参数提取与建模

铁电参数提取:

从P-V曲线提取Landau系数:

-

拟合P-V曲线:E=αP+βP3

-

提取α, β

-

计算微分电容:CFE=dP/dE

等效电路参数:

从S参数或Y参数提取:

-

小信号模型参数

-

本征参数:g_m, g_ds, C_gs, C_gd

-

寄生参数:R_g, R_s, R_d, L_g, L_s, L_d

温度依赖性:

变温测试提取:

-

活化能

-

温度系数

-

工作温度范围

10.1 多栅负电容晶体管

结构

示意图

铁电集成

优势

挑战

负电容FinFET

铁电包裹Fin

铁电层在栅堆叠

三维栅控,高密度

铁电保形沉积

负电容纳米片

铁电环绕纳米片

全环绕铁电层

最强栅控,可微缩

工艺复杂

负电容Gate-All-Around

铁电全环绕沟道

铁电全包裹

最佳静电控制

集成挑战

负电容隧道FET

铁电+隧穿结构

铁电极化增强隧穿

超低功耗,陡峭SS

工艺匹配

负电容负电容FET

串联负电容

多级负电容放大

极高增益

稳定性挑战

NC-FinFET设计要点:

-

Fin宽度<10nm以获得全耗尽

-

铁电厚度5-10nm

-

高k介质厚度1-2nm EOT

-

优化Fin高度/宽高比

NC-Nanosheet设计:

-

片厚度<5nm

-

片间距优化:考虑铁电沉积

-

铁电保形性:ALD最佳

-

应力工程:利用应变增强性能

10.2 异质集成

二维材料+NCFET:

-

二维材料(MoS₂, WSe₂)作为沟道

-

超薄体增强静电控制

-

范德华集成减少界面态

-

挑战:铁电与二维材料界面

铁电聚合物+NCFET:

-

PVDF-TrFE等铁电聚合物

-

低温工艺,柔性衬底兼容

-

透明,可拉伸

-

挑战:性能,稳定性

多铁性+NCFET:

-

铁电+铁磁多铁材料

-

电场控制磁性

-

自旋-电荷耦合器件

-

挑战:材料集成,工作温度

10.3 三维集成

单片三维NCFET:

-

多层堆叠NCFET

-

层间介质:低k材料

-

垂直互连:纳米硅通孔

-

热管理:散热通路设计

异质三维集成:

-

NCFET与CMOS堆叠

-

混合键合或单芯片集成

-

功能划分:逻辑+存储+传感

-

挑战:热,应力,工艺兼容

11.1 材料与集成挑战

挑战

描述

解决方案

进展

铁电厚度微缩

<5nm时铁电性消失

掺杂工程,应力工程

HZO可至5nm

界面质量

铁电/介质界面缺陷

界面层,表面处理

D_it<10¹¹ eV⁻¹cm⁻²

均匀性

晶圆内参数涨落

工艺优化,ALD沉积

均匀性<5%

CMOS兼容性

热预算,污染

后道集成,低温工艺

400°C工艺演示

疲劳耐久性

翻转次数限制

电极优化,掺杂

>10¹⁰次循环

温度稳定性

铁电性温度依赖

高T_C材料,设计补偿

HZO T_C~500°C

11.2 器件与电路挑战

挑战

描述

解决方案

进展

回滞控制

迟滞影响逻辑电路

电容匹配,厚度优化

无回滞器件演示

增益-带宽权衡

负电容与速度矛盾

铁电厚度优化,电路设计

f_T>300GHz演示

短期记忆

极化松驰导致记忆效应

材料优化,操作条件

保持时间>10年目标

统计变化

工艺引起的参数涨落

统计设计,冗余

统计模型建立

模型与EDA

缺乏准确模型和工具

紧凑模型开发,PDK

BSIM模型扩展

测试与验证

特殊测试需求

专用测试方案,BIST

测试芯片演示

11.3 系统级挑战

挑战

描述

解决方案

进展

功耗管理

动态负电容功耗

电路技术,电源门控

功耗降低30%演示

信号完整性

负电容可能引发振荡

稳定性设计,阻尼

稳定电路技术

热管理

铁电极化生热

热设计,散热通路

热分析工具

可靠性与老化

新失效机制

加速测试,寿命模型

可靠性标准制定

设计方法学

新器件设计流程

设计工具链,IP库

初步设计流程

成本效益

与传统CMOS竞争

增量集成,性能优势

成本分析进行中

12.1 近期发展(2023-2028)

目标

技术指标

关键突破

材料优化

HZO铁电性稳定,T_C>500°C,厚度<5nm

掺杂工程,应变工程

器件演示

SS<50mV/dec,无回滞,I_on>1mA/μm

界面工程,电容匹配

电路演示

千门级电路,>1GHz频率,功耗降低50%

设计方法,EDA工具

集成工艺

300mm晶圆工艺,CMOS兼容

低温工艺,后道集成

可靠性

10年寿命,>10¹⁰次翻转

材料优化,操作条件

12.2 中期发展(2028-2035)

目标

技术指标

关键突破

先进节点

5nm节点NCFET,3D集成

全环绕结构,异质集成

系统集成

处理器/存储器集成,混合信号系统

三维集成,设计自动化

新应用

神经形态计算,存算一体

多态存储,模拟计算

标准化

设计套件,模型,测试标准

产业协作,标准制定

产业化

特定应用产品(低功耗IoT等)

成本控制,供应链建立

12.3 长期愿景(2035-2050)

愿景

技术特征

潜在应用

后摩尔主力

2nm以下节点,三维单片集成

高性能计算,人工智能

智能系统

感存算一体,自适应系统

边缘智能,自主系统

量子-经典混合

负电容调控量子器件

量子计算接口,传感器

生物集成

低功耗生物接口

医疗植入,脑机接口

可持续计算

极低功耗,能量收集

无电池IoT,绿色计算

13.1 技术优势

-

突破玻尔兹曼极限:实现亚60mV/dec的亚阈值摆幅

-

低电压操作:可在<0.5V电压下工作,降低动态功耗

-

性能提升:相同电压下更高电流,或相同电流下更低电压

-

工艺兼容:HfO₂基铁电与CMOS工艺高度兼容

-

多功能性:逻辑、存储、神经形态计算统一平台

13.2 核心挑战

-

回滞控制:逻辑电路需要无回滞操作

-

可靠性:铁电疲劳、印记、保持等退化机制

-

稳定性:温度、频率、偏置稳定性

-

集成工艺:与先进节点CMOS工艺的集成挑战

-

设计方法:缺乏成熟的模型、EDA工具和设计方法

13.3 当前状态

-

材料:HZO铁电性成熟,5-10nm厚度可稳定工作

-

器件:SS<60mV/dec已多次演示,无回滞器件实现

-

电路:反相器、环形振荡器等基本电路演示

-

集成:300mm晶圆工艺开始研发

-

应用:低功耗逻辑、存储器为主要应用方向

13.4 未来方向

-

材料探索:新型铁电材料(二维铁电、聚合物铁电等)

-

结构创新:多栅、隧道、负电容组合器件

-

集成技术:三维集成、异质集成、单片集成

-

电路架构:存算一体、神经形态、近似计算

-

系统应用:物联网、边缘计算、生物医疗

负电容晶体管作为突破传统MOSFET功耗限制的最有前途技术之一,正从基础研究走向技术开发。随着材料、器件、集成、电路等各层面的不断突破,有望在未来低功耗电子系统中发挥关键作用。其发展需要跨学科合作,涵盖铁电物理、微纳加工、器件物理、电路设计等多个领域,最终实现从器件创新到系统应用的跨越。

1.1 基本定义与工作原理

光子晶体管是一种三端口(或更多端口)光学器件,其输出光信号的强度或相位受控制光信号的调制,实现光信号放大、开关和逻辑操作,功能上类比电子晶体管。

特性

电子晶体管

光子晶体管

根本差异

信息载体

电子(电荷)

光子(电磁波)

电荷 vs 无质量玻色子

相互作用

库仑力,散射

非线性光学效应

强 vs 弱相互作用

速度极限

载流子速度,RC延时

光速/材料中

ps-fs 级

功耗机制

焦耳热,充放电

吸收,散射,非线性损耗

本质更低理论极限

带宽潜力

~THz(受限渡越时间)

~100THz(光学频率)

高2-3个数量级

基本工作原理:控制光(栅极)改变非线性介质的光学性质(折射率n,吸收系数α),调制信号光(源-漏)的传输。

核心参量:

-

开关比:R=Pouton/Poutoff

-

调制深度:η=(Pouton−Poutoff)/Pincontrol

-

光学增益:G=Poutsignal/Pincontrol(需区分净增益与调制增益)

-

功耗:P=Pcontrol+Pbias+Ploss

-

响应时间:由非线性机制的时间常数决定

1.2 光学非线性理论框架

光子晶体管的核心是三阶非线性光学效应,用极化强度展开描述:

P(t)=ϵ0[χ(1)E(t)+χ(2)E2(t)+χ(3)E3(t)+⋯]

对于光子晶体管,最重要的非线性是三阶非线性:

P(3)(ω)=3ϵ0χ(3)(−ω;ω,ω,−ω)∣E(ω)∣2E(ω)

这导致折射率和吸收系数依赖于光强:

非线性折射率:

n(I)=n0+n2I

其中 n2=4ϵ0cn023Re(χ(3))(m²/W)

非线性吸收(包括饱和吸收与反饱和吸收):

α(I)=1+I/Isα0(饱和吸收)

或

α(I)=α0+βI(双光子吸收)

关键非线性过程:

-

交叉相位调制(XPM):控制光改变信号光的相位

Δϕsignal=λ2πn2IcontrolL

-

交叉吸收调制(XAM):控制光改变信号光的吸收

-

四波混频(FWM):产生新频率,可用于波长转换和放大

-

光学双稳态:非线性共振腔中的滞后效应,实现记忆功能

1.3 光与物质相互作用的量子描述

二能级系统模型(适用于原子、量子点、激子等):

哈密顿量:H=H0+Hint

其中相互作用项:

Hint=−μ⋅E(t)

μ是电偶极矩算符。

光学Bloch方程描述密度矩阵演化:

dtdρ21dtdρ11dtdρ22=−(iω21+γ2)ρ21+ℏiμ21E(t)(ρ11−ρ22)=−ℏiμ21E(t)(ρ21−ρ12∗)−γ1ρ11=ℏiμ21E(t)(ρ21−ρ12∗)+γ1ρ11

稳态解给出极化率:

χ(ω)=ϵ0ℏN∣μ21∣2(ω21−ω)2+γ22ω21−ω−iγ2⋅1+I/Is1

其中饱和强度 Is=2∣μ21∣2ϵ0cn0ℏ2γ1γ2

非线性增强策略:

-

共振增强:工作在原子/激子共振附近

-

场局域增强:等离激元、光子晶体腔

-

慢光增强:在结构中增加光与物质相互作用时间

2.1 按物理机制分类

类型

核心机制

非线性系数

速度

功耗

集成度

非线性光学型

材料本征χ³非线性

中等(10⁻¹⁸ m²/W)

飞秒

中等

中等

电光混合型

电光效应+电子控制

高(可调)

纳秒

高

高

等离激元型

表面等离激元共振

极高(10⁻¹⁶)

飞秒

高

低

激子型

激子-激子相互作用

高(共振)

皮秒

低

中等

光子晶体型

慢光增强非线性

增强10³-10⁶倍

皮秒

低

高

微腔型

腔增强非线性

极高(Q>10⁶)

皮秒

极低

中等

2.2 按结构分类

结构

示意图

工作原理

关键参数

波导型

信号与控制光在波导中共传

非线性相移积累

非线性系数,相互作用长度

腔型

光在腔内共振,控制光调谐共振

共振条件改变

品质因子Q,非线性系数

干涉型

MZI或Michelson干涉仪,控制光调相

相长/相消干涉

相移灵敏度,平衡度

吸收型

控制光改变吸收

饱和吸收/激发态吸收

吸收截面,恢复时间

分布式反馈型

周期性结构,控制光改变耦合条件

布拉格条件改变

耦合系数,长度

3.1 非线性光学波导型光子晶体管

基本结构:

控制光─────┐

├→非线性波导→信号输出

信号光─────┘

工作原理:交叉相位调制(XPM)或交叉吸收调制(XAM)

传输函数:

对于XPM主导的情况:

Pout=Pincos2(2Δϕ0+ΔϕNL)

其中

ΔϕNL=λ2πn2IcontrolLeff

有效长度 Leff=[1−exp(−αL)]/α

关键设计方程:

-

非线性相移:ϕNL=γPLeff,其中 γ=λAeff2πn2

-

开关条件:ϕNL=π时完全开关

-

开关功率:Pπ=γLeffπ

-

增益:G=∂Pcontrol∂Pout

典型材料参数:

材料

n₂ (m²/W)

非线性响应时间

线性损耗(dB/cm)

备注

Si

~5×10⁻¹⁸

飞秒(电子)

1-3

CMOS兼容

InGaAsP

~1×10⁻¹⁶

皮秒(载流子)

2-5

高非线性

ChG(硫系玻璃)

~2×10⁻¹⁷

飞秒(电子)

0.1-1

高非线性

AlGaAs

~1.5×10⁻¹⁷

飞秒(电子)

1-3

低双光子吸收

Si₃N₄

~2.5×10⁻¹⁹

飞秒(电子)

0.1-0.5

超低损耗

聚合物

~1×10⁻¹⁶

飞秒(电子)

0.5-2

可调谐

3.2 微腔/光子晶体腔型光子晶体管

基本原理:控制光改变腔的共振条件,影响信号光的传输

腔模方程:

耦合模理论描述:

dtda=(iΔω−τ1)a+iτe1sin

其中:

-

a:腔内场振幅

-

Δω=ω−ω0:失谐

-

τ:总衰减时间,1/τ=1/τ0+1/τe

-

τ0:固有衰减时间

-

τe:耦合衰减时间

-

sin:输入场

非线性频率漂移:

ΔωNL=−nω0n2Icavity=−Veffω0ϵ0cn2n2Ucavity

其中 Ucavity是腔内能量,Veff是有效模体积。

传输特性:

T=PinPout=(Δω+ΔωNL)2+(1/τ)2(1/τe)2

双稳态条件:

当非线性足够强时,输出呈现迟滞回线:

Δω=δ−nVeffω0n22ϵ0cn2∣a∣2

其中 δ是输入频率与腔共振的失谐。

关键参数优化:

-

品质因子Q:Q=ω0τ,高Q增强非线性但降低带宽

-

模式体积V_eff:小V_eff增强光场强度

-

非线性系数n₂:材料选择

-

耦合系数κ:临界耦合时效率最高

增强因子F:

相比于无腔情况,非线性增强因子为:

F=VeffQ⋅ncτ

典型光子晶体腔:Q∼106,Veff∼(λ/n)3,F∼106−109

3.3 等离激元增强型光子晶体管

基本原理:金属纳米结构中的表面等离激元共振产生极强的局域场增强

局域场增强因子:

L(ω)=E0Elocal2=ϵm(ω)+ϵd(ω)ϵd(ω)2

对于贵金属(Au, Ag),在可见-近红外波段,L可达10³-10⁶。

有效非线性系数增强:

χeff(3)=L2(ωp)L(ωs)L(ωc)χ(3)

其中ω_p, ω_s, ω_c分别是泵浦、信号、控制光频率。

等离激元共振条件:

对于球形纳米粒子:

Re[ϵm(ω)]=−2ϵd

对于棒状或复杂结构,可调谐到所需波长。

热效应与损伤阈值:

金属吸收导致热效应,限制最大光强:

ΔT=4πκRPabs

其中κ是热导率,R是粒子半径。

混合等离激元-介质结构:

结合金属的场增强和介质的低损耗:

-

金属-介质-金属波导

-

介质纳米线-金属结构

-

光子晶体-等离激元混合

3.4 激子型光子晶体管(基于半导体量子结构)

基本原理:激子(电子-空穴对)共振产生强光学非线性

激子共振非线性机制:

-

相空间填充:激子态被占据,降低吸收

-

带电激子效应:激子带电改变能级

-

激子-激子相互作用:激子间排斥/吸引

-

双激子形成:两个激子形成束缚态

非线性吸收模型:

α(I)=1+I/Isα0+βI

第一项为饱和吸收,第二项为双光子吸收。

激子饱和强度:

Is=2στℏω

其中σ是吸收截面,τ是激子寿命。

量子点/量子阱增强:

量子限制增强激子效应:

-

激子束缚能增加:Eb∝1/a2(a为尺寸)

-

振子强度增加:f∝1/a3

-

非线性增强:χ(3)∝f2/(Eb3Γ),Γ是线宽

典型材料与参数:

材料结构

激子束缚能(meV)

饱和强度(W/cm²)

响应时间

工作温度

GaAs量子阱

~10

10³-10⁴

~10 ps

低温

CdSe量子点

~100-200

10²-10³

~1 ps

室温

单层MoS₂

~500

10-100

~1 ps

室温

钙钛矿量子点

~100-300

10¹-10²

<1 ps

室温

有机染料分子

无束缚激子

10²-10³

fs-ps

室温

4.1 基本性能参数

参数

定义

理想值

当前记录

挑战

开关比

Pon/Poff

>100 dB

~30 dB

关态泄漏

插入损耗

10log(Pout/Pin)

<1 dB

3-10 dB

传播损耗

功耗

开关能量

<1 fJ/bit

10-100 fJ/bit

非线性效率

速度

开关时间

<1 ps

1-10 ps

载流子寿命

增益

Poutsignal/Pincontrol

>1 (净增益)

~0.1-0.5

损耗补偿

带宽

可调制频率范围

>1 THz

100-500 GHz

腔寿命限制

噪声系数

SNR_in/SNR_out

0 dB

3-10 dB

自发辐射

4.2 功率-速度权衡

基本限制:非线性相移需要能量和时间

ϕNL=λ2πn2IL=λ2πn2⋅AP⋅vgLτ

其中τ是脉冲宽度,v_g是群速度。

开关能量:

Eswitch=Pτ=2πn2ϕNLλA⋅Lvg

能量-时间积的下限:

量子光学极限:

Eτ≳σh或Eτ≳χ(3)ℏ

对于典型非线性材料,极限在aJ·ps量级。

品质因子(Figure of Merit):

FOM=αλn2或FOM=αλχ(3)

高FOM意味着高非线性、低损耗。

4.3 噪声与串扰

噪声来源:

-

散粒噪声:光子统计涨落,σP2=2hνPΔf

-

热噪声:热激发载流子,Pth=kTΔf

-

非线性噪声:自发四波混频、拉曼散射

-

串扰:相邻通道耦合,串扰比 XT=10log(Pcrosstalk/Psignal)

信噪比(SNR):

SNR=2hν(Psignal+PASE)Δf+σth2+σXT2Psignal2

误码率(BER):

对于OOK调制:

BER=21erfc(2Q),Q=σ1+σ0I1−I0

5.1 波导设计

非线性波导优化目标:

-

高非线性:大n₂,小A_eff

-

低损耗:小α

-

相位匹配:控制色散

-

低双光子吸收:尤其对电信波段

有效模面积:

Aeff=∫∣E∣4dA(∫∣E∣2dA)2

目标:最小化A_eff

色散管理:

群速度色散GVD:D=−λ22πcβ2

目标:在操作波长附近接近零色散,或特殊色散(反常色散)

典型波导结构:

结构

A_eff(μm²)

非线性系数γ (W⁻¹m⁻¹)

损耗(dB/cm)

特点

硅线波导

0.1-0.3

100-300

1-3

CMOS兼容,高非线性

Si₃N₄波导

1-3

1-3

0.1-0.5

超低损耗,中等非线性

Hydex玻璃波导

2-5

0.5-1

0.05-0.2

极低损耗

GaInP波导

0.3-0.8

200-500

2-5

高非线性,无TPA@1550nm

空芯波导

10-100

0.01-0.1

0.1-1

极低非线性,气体填充

色散工程:

通过几何设计控制色散:

-

宽度、高度变化

-

多层结构

-

光子晶体波导

-

狭缝波导

5.2 谐振腔设计

关键参数:

-

品质因子Q:Q=ω0τ=ω0/Δω

-

模式体积V_eff:Veff=max[ϵ(r)∣E(r)∣2]∫ϵ(r)∣E(r)∣2d3r

-

精细度F:F=ΔωFSR=1−RπR,R为反射率

共振条件:

环形谐振腔:2πRneff=mλ

法布里-珀罗腔:2nL=mλ

非线性增强因子:

F=VeffQ⋅nλ

典型值:微环Q~10⁶,V_eff~10(λ/n)³ ⇒ F~10⁵

光子晶体腔:

-

缺陷模:在光子带隙中引入缺陷形成局域模

-

高Q小V:Q可达10⁶,V_eff可接近(λ/n)³

-

设计方法:偶极子腔、L3腔、H1腔等

耦合设计:

临界耦合条件:κe=κ0(耦合损耗=固有损耗)

过耦合:κe>κ0,欠耦合:κe<κ0

5.3 有源增益集成

克服损耗实现净增益:

集成光学增益介质补偿损耗:

Gnet=exp[(Γg−α)L]

其中Γ是限制因子,g是增益系数。

集成方案:

-

半导体光放大器(SOA)集成:直接键合或外延生长

-

稀土离子掺杂:Er³⁺(1550nm)、Yb³⁺(1000nm)掺杂波导

-

III-V-on-Si异质集成:III-V材料键合到Si波导

-

量子点/量子阱集成:纳米结构增益介质

-

拉曼增益:利用受激拉曼散射

增益动态模型:

速率方程:

dtdN=qVI−τcN−vgg(N)S

dtdS=Γvgg(N)S−τpS+βτcN

其中β是自发辐射因子。

6.1 硅基光子晶体管制造流程

1. 衬底准备

a. SOI晶片:顶层Si 220nm,埋氧层2μm

b. 清洗:RCA标准清洗

c. 热氧化:生长10-20nm SiO₂缓冲层

2. 波导图案化

a. 电子束光刻或深紫外光刻

- 波导宽度:300-500nm

- 刻蚀深度:220nm(全刻蚀)或部分刻蚀

b. 反应离子刻蚀(RIE)

- 气体:HBr/Cl₂/O₂

- 选择比:Si:SiO₂ > 30:1

- 侧壁垂直度:>85°

c. 侧壁平滑处理

- 热氧化:生长/去除薄氧化层

- 化学机械抛光(CMP):可选

3. 非线性增强结构

a. 选择性区域掺杂(如有源区)

- 离子注入:P, As (n型) 或 B (p型)

- 快速热退火:激活掺杂

b. 量子点/量子阱集成

- 分子束外延生长

- 转移印刷或直接生长

c. 非线性材料沉积

- 硫系玻璃:PECVD或溅射

- 聚合物:旋涂+固化

- 二维材料:干法转移

4. 谐振腔制造

a. 微环/微盘谐振腔

- 电子束光刻定义

- 刻蚀:与波导同时或分别

- 半径:5-50μm

b. 光子晶体腔

- 电子束光刻定义空气孔阵列

- 孔半径:~100nm,晶格常数:~400nm

- 刻蚀:高深宽比,侧壁平滑

c. 法布里-珀罗腔

- 波导端面抛光:垂直度<0.1°

- 介质镜沉积:SiO₂/Ta₂O₅多层膜

5. 金属结构(如适用)

a. 等离激元结构

- 电子束光刻定义金属纳米结构

- 金属沉积:Au, Ag, 5-50nm

- 剥离或刻蚀

b. 电极(电光型)

- 金属沉积:Ti/Au, Cr/Au

- 光刻+刻蚀定义电极

6. 包层与钝化

a. SiO₂上包层沉积

- PECVD:300nm SiO₂

- 退火:400°C,N₂退火减小应力

b. 开窗:接触孔或耦合区

c. 钝化:Si₃N₄或Al₂O₃沉积

7. 光栅耦合器(片上耦合)

a. 光栅刻蚀:周期~630nm,深度~70nm

b. 倾斜角度:~10°,优化耦合效率

c. 抗反射涂层:减少背向反射

8. 测试与封装

a. 端面抛光:用于端面耦合

b. 光纤阵列对准键合

c. 热电冷却器集成(温度控制)

d. 电学引线键合

6.2 异质集成技术

技术

原理

优点

挑战

直接键合

表面活化键合

高质量,低损耗

表面平整度要求高

转移印刷

印章转移

材料选择自由,低温

对准精度,成品率

外延生长

异质外延

单片集成,高质量

晶格失配,热失配

晶圆键合

中介层键合

高良率,大面积

热膨胀系数匹配

二维材料转移

干法/湿法转移

超薄,柔性

污染,皱褶

III-V-on-Si集成示例:

-

III-V晶片生长增益层

-

Si波导制备

-

晶片键合(直接或中介层)

-

III-V衬底去除

-

III-V有源区图案化

-

电极制备

6.3 关键工艺参数优化

工艺步骤

关键参数

优化目标

典型值/范围

波导刻蚀

侧壁粗糙度,刻蚀深度,垂直度

低散射损耗,模式控制

粗糙度<2nm RMS,垂直度>85°

非线性材料集成

厚度,均匀性,界面质量

高非线性,低界面损耗

厚度控制±5%,均匀性>95%

谐振腔制造

Q因子,模式体积,耦合

高Q,小V_eff,临界耦合

Q>10⁶,V_eff~3(λ/n)³

金属结构

尺寸精度,表面粗糙度

等离激元共振控制,低损耗

尺寸误差<5nm,粗糙度<1nm

封装耦合

耦合效率,对准精度

高耦合效率,低回波损耗

效率>50%,回波损耗<-40dB

7.1 基本逻辑门实现

逻辑门

实现方案

工作原理

真值表

光学NOT门

MZI+非线性相移

控制光诱导π相移

输入0→输出1,输入1→输出0

光学AND门

非线性环镜

两路输入相长干涉

1,1→1,其他→0

光学OR门

非线性定向耦合

任一输入开启开关

0,0→0,其他→1

光学XOR门

干涉仪+交叉相位调制

两路输入比较

相同→0,不同→1

光学NAND门

级联NOT和AND

组合逻辑

AND后取反

光学锁存器

双稳态腔

光学双稳态

保持状态

光学触发器

耦合双稳态腔

时钟控制状态切换

边沿触发

全光逻辑门的挑战:

-

扇出问题:一个门驱动多个后续门

-

级联损耗:多级级联后信号衰减

-

同步问题:光信号定时

-

逻辑电平恢复:每级后信号整形

7.2 光计算架构

数字光计算:

-

布尔逻辑门阵列

-

光互连网络

-

光存储元件

-

挑战:功耗、集成度、可扩展性

模拟光计算:

-

光学矩阵乘法:利用MZI阵列

-

光学神经网络:光突触权重

-

光学信号处理:滤波、卷积

-

优势:并行性、高速、低功耗

光神经形态计算:

-

光脉冲神经元:基于激光器或非线性腔

-

光突触:可调谐耦合器或相变材料

-

光神经网络:全光实现前向和反向传播

-

优势:高速、低功耗、并行

存内计算:

-

光学存储器控制计算

-

减少数据移动能耗

-

光学内容可寻址存储器

-

光学随机存取存储器

7.3 光互连与片上网络

片内光互连:

-

波导网络:全局通信

-

光路由器:MZI开关阵列

-

仲裁与流控:光控制信号

-

优势:高带宽、低延迟、低串扰

芯片间光互连:

-

光I/O:光栅耦合器或端面耦合

-

多路复用:波分、模分、时分复用

-

时钟分配:光时钟分布网络

-

优势:高密度、低功耗

三维光互连:

-

垂直光耦合:光栅或反射镜

-

多层光网络:减少布线拥塞

-

优势:更高带宽密度

8.1 线性光学表征

测试

参数

方法

设备

传输谱

插入损耗,带宽

可调谐激光器+光功率计

TLS,可调激光器,光谱分析仪

反射谱

反射率,回波损耗

光循环器+探测器

OSA,光反射计

模态分析

模场,有效折射率

近场扫描,傅里叶空间成像

近场光学显微镜

损耗测量

传播损耗,耦合损耗

截断法,光时域反射

OTDR,高精度功率计

色散测量

群速度色散,色散斜率

白光干涉,频谱相位干涉

干涉仪,频率分辨光学门

偏振特性

偏振相关损耗,双折射

偏振控制器+分析仪

偏振分析仪

8.2 非线性特性表征

测试

参数

方法

设备

非线性折射率n₂

n₂值,响应时间

Z扫描,自相位调制

飞秒激光,Z扫描装置

非线性吸收

双光子吸收系数β

开孔Z扫描,透射测量

可调谐光源,锁相放大器

四波混频效率

转换效率,带宽

双光源泵浦-探测

两个可调谐激光器,光谱仪

饱和强度

饱和光强I_s

强度依赖透射测量

可调衰减器,功率计

非线性相移

相移与功率关系

干涉测量,MZI

干涉仪,相位解调

双稳态特性

迟滞回线,开关阈值

扫描波长/功率,记录透射

可调激光器,高速探测器

Z扫描技术:

测量透过率随样品位置变化:

-

闭孔Z扫描:提取n₂

-

开孔Z扫描:提取β

-

拟合公式:T(z)=1−(z2/z02+9)(z2/z02+1)4Δϕ0z/z0

其中 Δϕ0=(2π/λ)n2I0Leff

自相位调制法:

测量光谱展宽:

Δωmax=cτω0n2I0Leff

从展宽计算n₂。

8.3 动态特性测试

测试

参数

方法

设备

开关速度

上升/下降时间,开关时间

泵浦-探测,强度调制

飞秒激光,条纹相机

恢复时间

载流子寿命,热恢复时间

泵浦-探测,时间分辨测量

飞秒激光,光学延迟线

调制响应

小信号频率响应

强度调制+矢量网络分析

矢量网络分析仪,电光调制器

误码率

BER vs 功率,眼图

伪随机码测试

误码率测试仪,采样示波器

噪声特性

相对强度噪声,相位噪声

光谱分析,平衡探测

光谱分析仪,平衡探测器

热特性

热光系数,热响应时间

加热器调制,热成像

热电冷却器,红外相机

泵浦-探测技术:

-

泵浦脉冲激发非线性

-

探测脉冲延迟探测

-

测量透过率变化ΔT/T

-

时间分辨率可达飞秒级

9.1 基础物理挑战

挑战

描述

影响

解决方案

非线性效率低

材料χ³小,需要高功率

功耗高,热效应

谐振增强,慢光,等离激元局域

双光子吸收

虚中间态被共振吸收

损耗,载流子产生

带隙工程,非共振工作,新材料

热效应

吸收导致温升

折射率变化,不稳定

热管理,低吸收材料,脉冲工作

串扰

信道间非线性耦合

信号干扰,误码

波长管理,偏振正交,时空隔离

相位匹配

动量不匹配限制效率

低转换效率

准相位匹配,波导色散工程,周期极化

噪声

非线性噪声积累

SNR降低

滤波,相位共轭,噪声抑制技术

9.2 材料与制造挑战

挑战

描述

影响

解决方案

材料损耗

吸收,散射,辐射损耗

插入损耗高

材料纯化,表面平滑,优化设计

制造公差

尺寸偏差,粗糙度

性能波动,成品率低

先进光刻,后处理,容差设计

集成兼容性

不同材料热/机械失配

应力,缺陷,可靠性

缓冲层,应变工程,异质集成

可扩展性

大规模集成困难

成本高,复杂度高

标准化工艺,晶圆级制造

封装耦合

光纤-芯片耦合损耗

系统损耗大

光栅耦合器,端面耦合优化

长期稳定性

材料退化,污染

性能漂移,寿命短

钝化层,封装,环境控制

9.3 系统级挑战

挑战

描述

影响

解决方案

功耗

非线性操作需要功率

能效低,发热

谐振增强,新材料,脉冲操作

扇出能力

一个门驱动多个门

信号衰减,速度降低

光放大,再生,缓冲器

级联性

多级连接损耗积累

可扩展性受限

集成增益,低损耗设计,再生

时钟分配

同步多个光门

时序问题,时钟偏移

光时钟树,锁相环,同步电路

测试验证

复杂光路测试

测试成本高,时间长

内置测试,自动化测试平台

设计工具

缺乏EDA工具

设计周期长,优化困难

开发专用光子设计自动化工具

10.1 近期应用(1-3年)

应用领域

具体应用

技术需求

发展状态

光通信

全光信号再生,波长转换

高非线性,低功耗

实验室演示,部分商用

光互连

芯片内/芯片间光互连

低损耗波导,高速调制

研究向产品过渡

光计算

光学矩阵乘法,卷积加速

可编程MZI阵列,低损耗

实验室演示

量子信息

单光子开关,量子门

单光子非线性,低噪声

基础研究

传感

非线性增强传感器

高Q腔,灵敏检测

实验室演示

10.2 中期应用(3-10年)

应用领域

具体应用

技术需求

发展状态

光逻辑电路

基本逻辑门,简单处理器

低功耗,高集成度

原型演示

神经形态计算

光神经网络,脉冲神经网络

可调谐突触,光神经元

早期研究

微波光子学

微波信号处理,光子ADC

宽带宽,线性调制

实验室演示

量子计算

光量子计算节点

高保真度,可扩展

基础研究

生物光子学

细胞内光操作,成像

低功率,生物兼容

探索阶段

10.3 长期愿景(10年以上)

愿景

技术特征

潜在应用

全光计算机

全光CPU,光存储,光互连

超高速计算,人工智能

光子大脑

类脑光计算,光神经网络

认知计算,模式识别

全球光网络

全光路由,光分组交换

全球通信,物联网

量子互联网

量子中继,量子网络

安全通信,分布式量子计算

生物-光子接口

光与生物系统直接交互

脑机接口,细胞控制

10.4 技术路线图

时间

非线性效率

开关能量

速度

集成度

应用

2023-2025

提高10倍

100 fJ/bit

10 ps

10³个器件

专用加速器

2025-2030

提高100倍

10 fJ/bit

1 ps

10⁵个器件

光协处理器

2030-2035

提高1000倍

1 fJ/bit

100 fs

10⁷个器件

全光处理器

2035+

接近量子极限

0.1 fJ/bit

10 fs

10⁹个器件

光量子计算机

11.1 技术优势总结

-

超高速度:潜在THz级操作,远超电子器件

-

低串扰:光子间相互作用弱,信道隔离好

-

宽带宽:光学频率提供极大带宽

-

低功耗:理论上可突破电子器件功耗极限

-

并行性:波长、偏振、模式等多维度复用

-

抗电磁干扰:光子不受电磁场直接影响

-

与光纤兼容:直接与通信网络连接

11.2 核心挑战总结

-

非线性效率:光非线性比电子相互作用弱多个数量级

-

集成规模:光子器件尺寸受衍射极限限制

-

功耗:虽然理论低,但实际系统功耗仍高

-

可编程性:光器件重构比电子困难

-

存储:光学存储仍不成熟

-

放大:全光放大仍有挑战

-

标准化:缺乏统一的设计、制造、测试标准

11.3 关键突破方向

-

新材料:高非线性、低损耗新材料探索

-

新机制:量子非线性、拓扑光子学、非厄米光学

-

新结构:超构表面、拓扑腔、非互易结构

-

新集成:异质集成、三维集成、混合集成

-

新架构:存算一体、类脑计算、量子-经典混合

11.4 与电子技术的协同发展

光子晶体管不会完全取代电子晶体管,而是互补发展:

混合光电集成:

-

电子用于存储、控制、低速逻辑

-

光子用于通信、高速处理、互连

-

各自发挥优势,协同工作

光电融合芯片:

-

光I/O,电计算

-

光互连,电存储

-

光计算,电控制

未来发展路径:

-

先解决光互连,降低通信能耗

-

发展光加速器,专用于矩阵运算等

-

探索全光计算,特定应用突破

-

最终实现光电融合的下一代信息处理系统

光子晶体管代表了突破传统电子计算极限的重要方向,虽然面临诸多挑战,但在材料、器件、集成、架构等各方面的持续进步下,有望在未来特定应用领域发挥关键作用,并与电子技术共同推动信息技术的下一次革命。

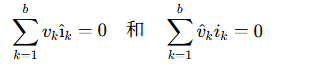

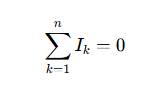

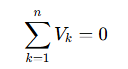

1.1 电路基本定律

基尔霍夫定律:

-

KCL(电流定律):任一节点电流代数和为零

-

KVL(电压定律):任一回路电压代数和为零

特勒根定理(功率守恒):

对于两个具有相同拓扑结构的电路N和N̂,有

对偶原理:

电路方程在特定变换下保持形式不变,如:

-

电压↔电流

-

电阻↔电导

-

电感↔电容

-

串联↔并联

-

网孔分析↔节点分析

1.2 线性电路分析方法

节点电压法:

对于n个节点的电路,有(n-1)个独立KCL方程:

YVn=Is

其中Y是节点导纳矩阵,V_n是节点电压向量,I_s是等效电流源向量。

网孔电流法:

对于m个网孔的电路,有m个独立KVL方程:

ZIm=Vs

其中Z是网孔阻抗矩阵,I_m是网孔电流向量,V_s是等效电压源向量。

叠加定理:

线性电路中,多个独立源共同作用产生的响应等于各独立源单独作用时响应的代数和。

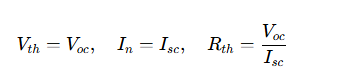

戴维南-诺顿等效:

任何线性有源单端口网络可等效为:

-

戴维南:电压源V_th串联电阻R_th

-

诺顿:电流源I_n并联电导G_n

其中:

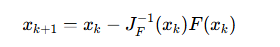

1.3 非线性电路分析方法

牛顿-拉夫森法:

解非线性方程F(x)=0:

其中J_F是雅可比矩阵。

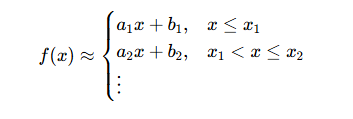

分段线性化:

将非线性特性用分段线性函数近似:

小信号分析:

在工作点附近线性化:

小信号模型只保留一阶项。

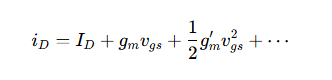

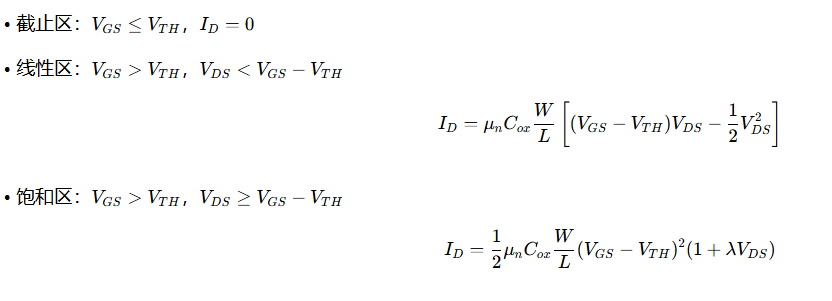

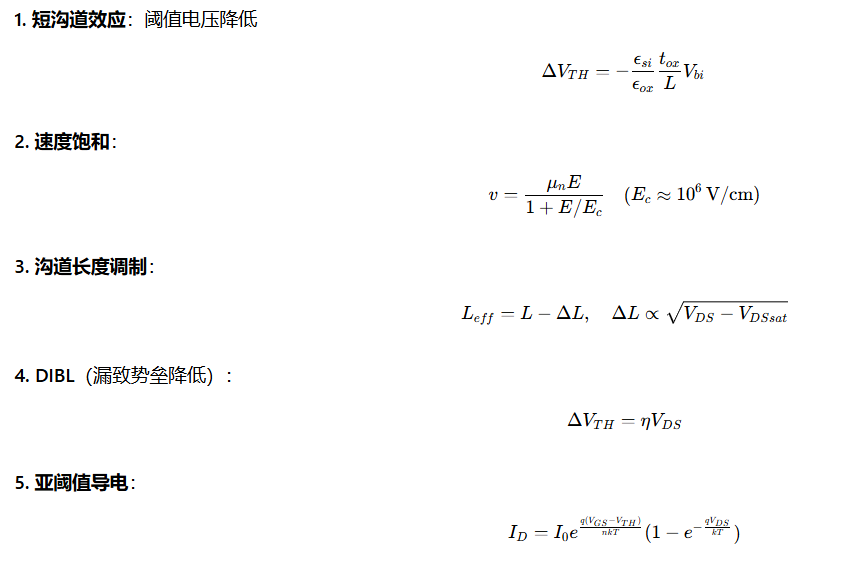

2.1 MOS晶体管模型

平方律模型(长沟道):

BSIM模型系列:

-

BSIM1:基本电荷守恒模型

-

BSIM3v3:包含短沟道效应、窄宽度效应、速度饱和等

-

BSIM4:增加栅极隧穿电流、应力效应等

-

BSIM-CMG:FinFET和纳米线晶体管模型

-

BSIM-IMG:超薄体SOI模型

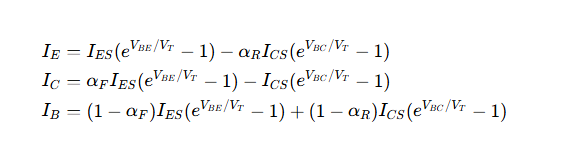

高级效应建模:

Ebers-Moll模型:

Gummel-Poon模型(更精确):

包含:

-

基区宽度调制(Early效应)

-

基区扩展电阻

-

电荷存储效应

-

高注入效应

小信号模型(混合π模型):

参数:

-

跨导:gm=IC/VT

-

输入电阻:rπ=β/gm

-

输出电阻:ro=VA/IC(Early电压V_A)

-

基极电阻:rb

-

集电极-基极电容:Cμ

-

发射结电容:Cπ

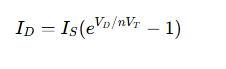

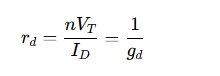

2.3 二极管模型

肖克利方程:

其中:

-

IS:饱和电流

-

n:发射系数(1-2)

-

VT=kT/q:热电压

小信号电阻:

电荷存储效应:

2.4 温度效应模型

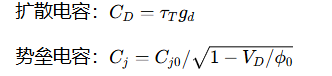

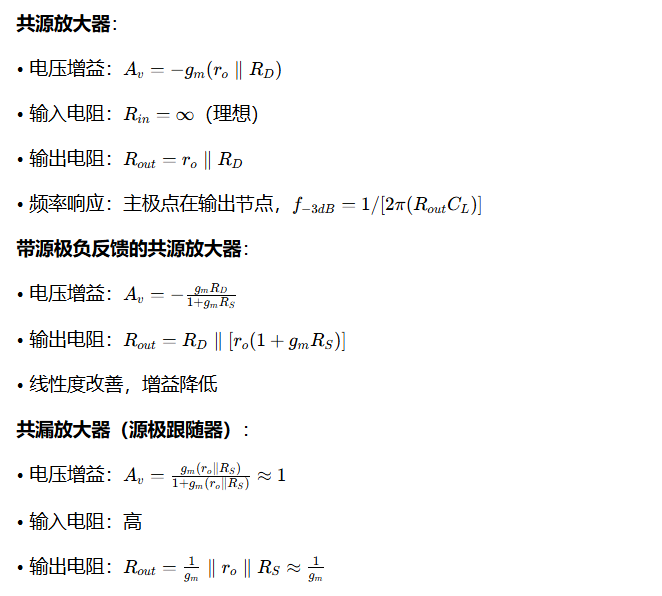

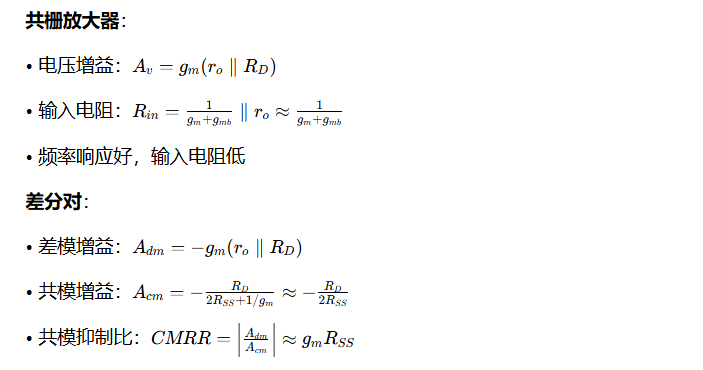

3.1 单级放大器

共源放大器:

-

电压增益:Av=−gm(ro∥RD)

-

输入电阻:Rin=∞(理想)

-

输出电阻:Rout=ro∥RD

-

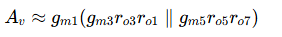

频率响应:主极点在输出节点,f−3dB=1/[2π(RoutCL)]

带源极负反馈的共源放大器:

-

电压增益:Av=−1+gmRSgmRD

-

输出电阻:Rout=RD∥[ro(1+gmRS)]

-

线性度改善,增益降低

共漏放大器(源极跟随器):

-

电压增益:Av=1+gm(ro∥RS)gm(ro∥RS)≈1

-

输入电阻:高

-

输出电阻:Rout=gm1∥ro∥RS≈gm1

共栅放大器:

-

电压增益:Av=gm(ro∥RD)

-

输入电阻:Rin=gm+gmb1∥ro≈gm+gmb1

-

频率响应好,输入电阻低

差分对:

-

差模增益:Adm=−gm(ro∥RD)

-

共模增益:Acm=−2RSS+1/gmRD≈−2RSSRD

-

共模抑制比:CMRR=AcmAdm≈gmRSS

3.2 电流镜与偏置电路

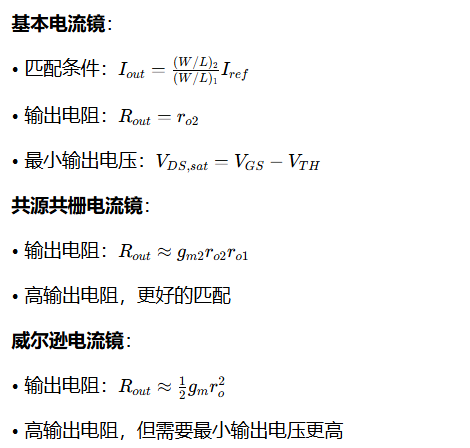

基本电流镜:

-

匹配条件:Iout=(W/L)1(W/L)2Iref

-

输出电阻:Rout=ro2

-

最小输出电压:VDS,sat=VGS−VTH

共源共栅电流镜:

-

输出电阻:Rout≈gm2ro2ro1

-

高输出电阻,更好的匹配

威尔逊电流镜:

-

输出电阻:Rout≈21gmro2

-

高输出电阻,但需要最小输出电压更高

偏置电路设计原则:

-

电源无关:偏置电流不随电源电压变化

-

温度稳定:偏置电流对温度不敏感

-

工艺不敏感:对工艺变化鲁棒

-

启动电路:防止零电流状态

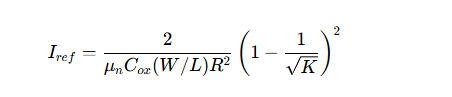

恒跨导偏置:

使gm恒定,不随工艺和温度变化:

其中K是电流镜比例。

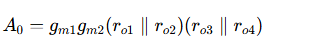

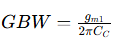

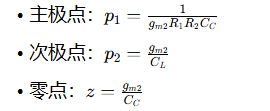

3.3 运算放大器设计

性能指标:

-

直流增益:

-

增益带宽积:

-

相位裕度:通常要求>60°

-

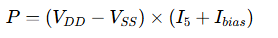

转换速率:SR=CCI5

-

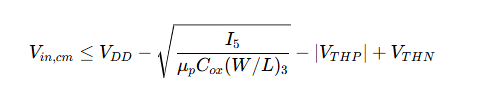

共模输入范围:

-

输出摆幅:轨到轨或接近电源轨

-

功耗:

-

噪声:输入参考噪声

-

失调电压:系统失调和随机失调

两级运放设计:

-

第一级:差分输入,高增益

-

第二级:共源放大,大摆幅

-

频率补偿:米勒补偿CC

-

零极点:

折叠式共源共栅运放:

-

高增益:

-

高输出摆幅

-

频率补偿复杂

轨到轨输入/输出运放:

-

输入级:并联NMOS和PMOS差分对

-

输出级:AB类输出,大摆幅

-

恒定跨导设计

3.4 反馈理论

反馈类型:

类型

采样

混合

增益表达式

输入电阻

输出电阻

串联-并联

电压

电压

Af=1+AβA

增加(1+Aβ)

减小1/(1+Aβ)

并联-串联

电流

电流

Af=1+AβA

减小1/(1+Aβ)

增加(1+Aβ)

串联-串联

电流

互阻

Af=1+AβA

增加(1+Aβ)

增加(1+Aβ)

并联-并联

电压

互导

Af=1+AβA

减小1/(1+Aβ)

减小1/(1+Aβ)

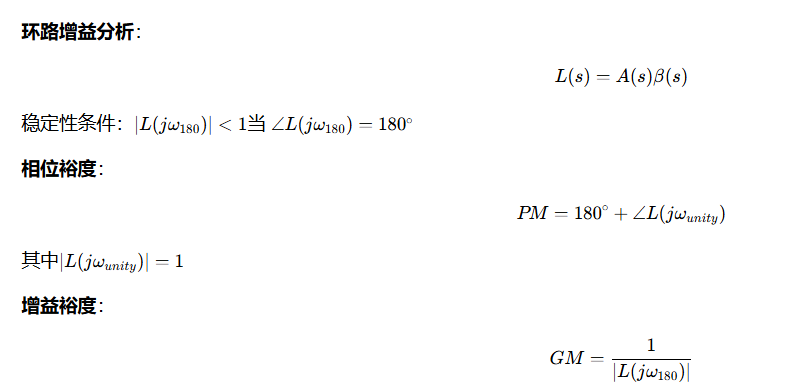

环路增益分析:

L(s)=A(s)β(s)

稳定性条件:∣L(jω180)∣<1当 ∠L(jω180)=180∘

相位裕度:

PM=180∘+∠L(jωunity)

其中∣L(jωunity)∣=1

增益裕度:

GM=∣L(jω180)∣1

频率补偿技术:

-

主极点补偿:在原点或低频引入主极点

-

米勒补偿:利用米勒效应将大电容等效为输入端的大电容

-

超前补偿:引入零点抵消极点

-

嵌套米勒补偿:多级运放补偿

3.5 比较器

开环比较器:

-

高增益放大器

-

失调电压:随机失调和系统失调

-

迟滞:防止噪声误触发

-

响应时间:由带宽和压摆率决定

时钟比较器:

-

动态比较器:预充电和比较阶段

-

锁存比较器:正反馈加速

-

亚稳态:当输入差很小时,输出延迟增加

比较器性能参数:

-

分辨率(最小可检测电压差)

-

速度(传播延迟)

-

功耗

-

失调电压

-

输入共模范围

-

噪声

4.1 CMOS逻辑门

静态CMOS逻辑:

-

上拉网络(PMOS):实现逻辑函数的反

-

下拉网络(NMOS):实现逻辑函数

-

逻辑努力:g=Cin,gate/Cin,inv

-

本征延迟:p=RCint/τ,τ是工艺特征时间

逻辑努力理论:

路径延迟:D=∑gihi+∑pi

其中hi=Cout,i/Cin,i是电气努力

最优级努力:f=gihi=F1/N,其中F=∏hi,N是级数

动态CMOS逻辑:

-

预充电阶段:输出预充电到VDD

-

求值阶段:根据输入求值

-

优点:速度快,晶体管数少

-

缺点:电荷分享,噪声容限低

传输管逻辑:

-

用传输管作为开关

-

适用于多路选择器等

-

电平恢复问题

4.2 时序电路

锁存器:

-

电平敏感

-

透明锁存器:当时钟有效时,输出跟随输入

-

建立时间tsetup和保持时间thold

触发器:

-

边沿触发

-

主从结构

-

建立时间、保持时间、时钟到输出延迟tCQ

时序分析:

关键路径延迟:Tc=max(tpath,i)

时钟频率:fmax=1/Tc

时间裕量:slack=Tc−trequired

时钟偏差:

Tc≥tpd,logic+tsetup+tskew

保持时间约束:tcd,logic≥thold−tskew

4.3 存储器电路

SRAM单元(6T):

-

两个交叉耦合反相器

-

两个访问晶体管

-

静态噪声容限(SNM)

-

读写稳定性分析

DRAM单元(1T1C):

-

一个晶体管,一个电容

-

需要刷新

-

破坏性读取

非易失存储器:

-

Flash:浮栅晶体管

-

MRAM:磁性隧道结

-

RRAM:电阻切换

-

PCRAM:相变材料

存储器架构:

-

存储单元阵列

-

地址译码器

-

读写放大器

-

控制逻辑

4.4 低功耗设计

功耗组成:

-

动态功耗:

Pdynamic=αCVDD2f

-

短路功耗:

Pshort=ImeanVDD

-

静态功耗:

-

亚阈值漏电:Isub=I0e(VGS−VTH)/nVT

-

栅极漏电:IG=IG0e−tox/λ

-

结漏电:Ij=Is(eVj/VT−1)

-

低功耗技术:

-

电源门控:关断闲置模块电源

-

时钟门控:关断闲置模块时钟

-

多电压域:不同模块用不同电压

-

动态电压频率调整(DVFS):根据负载调整电压频率

-

亚阈值电路:在亚阈值区工作

-

近阈值计算:在阈值电压附近工作

5.1 ADC性能参数

静态参数:

-

分辨率:N位

-

积分非线性(INL):实际传输特性与理想直线的最大偏差

-

微分非线性(DNL):相邻码的步长与1LSB的偏差

-

失调误差:零点偏移

-

增益误差:满量程误差

动态参数:

-

信噪比(SNR):SNR=6.02N+1.76dB

-

信纳比(SINAD):信号与(噪声+谐波)的功率比

-

有效位数(ENOB):ENOB=(SINAD−1.76)/6.02

-

无杂散动态范围(SFDR):基波与最大谐波的功率比

-

总谐波失真(THD):谐波总功率与基波功率比

5.2 ADC架构

Flash ADC:

-

2^N-1个比较器

-

编码逻辑

-

优点:最快

-

缺点:面积大,功耗高,输入电容大

-

适用于高速低分辨率

Pipeline ADC:

-

多级流水线

-

每级包含采样保持、子ADC、DAC、减法器、增益级

-

优点:高速高分辨率折中

-

缺点:数字误差校正复杂

-

运放要求高

逐次逼近型(SAR) ADC:

-

二进制搜索算法

-

包含比较器、DAC、SAR逻辑

-

优点:低功耗,中等速度

-

缺点:速度受DAC建立时间限制

-

适用于中速中高分辨率

Delta-Sigma ADC:

-

过采样和噪声整形

-

包含调制器、数字滤波器

-

优点:高分辨率,对模拟元件要求低

-

缺点:速度慢

-

适用于高分辨率低频应用

5.3 DAC设计

电阻型DAC:

-

串联电阻分压

-

R-2R梯形网络

-

优点:单调性好

-

缺点:电阻匹配要求高

电容型DAC:

-

电荷再分配

-

优点:功耗低,匹配性好

-

缺点:速度受开关限制

-

常用于SAR ADC

电流舵DAC:

-

电流源阵列

-

优点:速度快

-

缺点:面积大,功耗高

-

需要校准改善线性度

DAC性能参数:

-

建立时间:输出稳定在误差范围内的时间

-

毛刺能量:转换时的瞬态能量

-

动态线性度:SFDR,IMD

6.1 低噪声放大器(LNA)

性能指标:

-

噪声系数(NF):NF=10log(F),F=SNRoutSNRin

-

增益:功率增益S21

-

输入匹配:S11

-

线性度:IIP3,P1dB

-

稳定性:无条件稳定条件K>1,∣Δ∣<1

-

功耗

源极负反馈LNA:

-

输入匹配:Zin=jωLg+jωCgs1+CgsgmLs

-

实现50Ω匹配

-

噪声系数优化

噪声系数:

对于共源放大器:

F=1+RsRg+αγωTω0gmRs(ωTω0)2

其中γ是噪声系数,α=g_m/g_d0,ω_T是特征频率。

IIP3计算:

对于弱非线性系统:

IIP3=34a3a1

其中a_1是线性增益系数,a_3是三阶非线性系数。

6.2 混频器

性能指标:

-

转换增益:Gc=PRF,inPIF,out

-

噪声系数

-

线性度:IIP2,IIP3

-

端口隔离:LO-RF,LO-IF,RF-IF

-

LO驱动功率

吉尔伯特单元混频器:

-

双平衡结构

-

高线性度

-

良好隔离

-

转换增益:Gc=π2gmRL

噪声系数:

单平衡混频器:F=1+α4γ+α4Rggm

双平衡混频器:噪声更低,但需要更高LO功率

6.3 压控振荡器(VCO)

性能指标:

-

相位噪声:L(Δf)=10log(PcarrierPsideband(Δf))

-

调谐范围

-

功耗

-

输出幅度

-

谐波抑制

相位噪声模型(Leeson模型):

L(Δf)=10log[Psig2FkT(1+4Q2Δf2f02)(1+∣Δf∣Δf1/f3)]

其中:

-

F:噪声系数

-

k:玻尔兹曼常数

-

T:温度

-

P_sig:信号功率

-

f_0:振荡频率

-

Q:品质因数

-

Δf_1/f3:闪烁噪声转角频率

LC振荡器:

-

交叉耦合对提供负阻

-

频率:f0=2πLC1

-

调谐:变容二极管

-

相位噪声好,但调谐范围窄

环形振荡器:

-

N级反相器环

-

频率:f0=2Ntd1

-

调谐:调节延迟

-

调谐范围宽,但相位噪声差

7.1 低压差稳压器(LDO)

基本结构:

-

误差放大器

-

功率管(PMOS或NMOS)

-

反馈电阻网络

-

频率补偿网络

性能参数:

-

压差电压:Vdropout=Vin−Vout,min

-

负载调整率:ΔIloadΔVout

-

线性调整率:ΔVinΔVout

-

电源抑制比(PSRR):

PSRR(f)=20logAfeedthrough(f)AEA(f)

-

噪声

-

静态电流

频率补偿:

-

主极点:在误差放大器输出

-

次极点:在LDO输出

-

零点:ESR零点或前馈补偿

-

要求:相位裕度>60°

7.2 DC-DC转换器

降压转换器(Buck):

-

开关频率f_s

-

占空比:D=VinVout

-

电感电流纹波:ΔIL=Lfs(Vin−Vout)D

-

输出电压纹波:ΔVout=8CfsΔIL

升压转换器(Boost):

-

占空比:D=1−VoutVin

-

电感电流纹波:ΔIL=LfsVinD

-

输出电压纹波:ΔVout=CfsIoutD

控制模式:

-

电压模式:反馈电压与参考比较,控制占空比

-

电流模式:内环控制电感电流,外环控制电压

-

更好的动态响应

-

自动过流保护

-

需要斜坡补偿防止次谐波振荡

-

效率:

η=PinPout=VinIinVoutIout

损耗来源:开关损耗、导通损耗、驱动损耗、静态损耗

8.1 仿真类型

直流分析(DC Analysis):

-

工作点分析

-

直流传输特性

-

灵敏度分析

-

蒙特卡洛分析

交流分析(AC Analysis):

-

小信号频率响应

-

噪声分析

-

稳定性分析(环路增益、相位裕度)

-

阻抗分析

瞬态分析(Transient Analysis):

-

时域响应

-

大信号特性

-

开关波形

-

建立时间、保持时间

参数扫描(Parameter Sweep):

-

温度扫描

-

工艺角分析

-

尺寸扫描

-

电压扫描

蒙特卡洛分析(Monte Carlo):

-

工艺偏差

-

器件失配

-

统计特性

-

成品率预测

8.2 模型与仿真精度

器件模型层次:

-

物理模型:基于物理方程,精度高,速度慢

-

紧凑模型:基于半经验公式,精度和速度平衡

-

查表模型:基于仿真或测试数据,速度快,精度取决于数据密度

-

行为级模型:描述功能,速度快,用于系统仿真

工艺角分析:

-

典型-典型(TT)

-

快-快(FF)

-

慢-慢(SS)

-

快-慢(FS)

-

慢-快(SF)

-

考虑温度:-40°C, 27°C, 125°C

失配分析:

-

随机失配:Pelgrom模型

σ2(ΔP)=WLAP2+SP2D2

其中A_P是失配系数,S_P是间距相关系数

-

系统失配:版图梯度,温度梯度

8.3 后仿真与验证

寄生参数提取:

-

电阻提取:方块电阻,接触电阻

-

电容提取:层间电容,边缘电容,耦合电容

-

电感提取:高频时重要

-

衬底耦合:通过衬底的耦合

信号完整性分析:

-

串扰:耦合电容和互感引起

Vvictim=Cc+CvCcVaggressor

-

IR压降:电源网络电压降

-

地弹:开关电流引起地线波动

-

电磁干扰(EMI):高频辐射

可靠性分析:

-

电迁移:电流密度限制

MTTF∝J−neEa/kT

-

热分析:结温计算

-

闩锁效应:寄生BJT导通

-

ESD保护:HBM,CDM,MM模型

9.1 版图基础

设计规则(Design Rules):

-

最小线宽

-

最小间距

-

最小覆盖

-

最小面积

-

天线规则

-

密度规则

匹配技术:

-

相同方向:所有器件相同方向放置

-

对称布局:差分对对称布局

-

共同质心:抵消梯度影响

-

虚拟器件:边界条件一致

-

交叉耦合:交叉指型,同心圆

寄生效应最小化:

-

电阻:短而宽,多个接触孔

-

电容:远离高频信号线,屏蔽

-

电感:避免电流回路,使用差分对

-

衬底噪声:保护环,隔离

9.2 模拟版图技巧

器件匹配:

-

晶体管匹配:

-

相同W/L

-

相同方向

-

相同环境

-

交叉耦合

-

-

电阻匹配:

-

相同材料

-

相同宽度

-

相同走向

-

虚拟电阻

-

-

电容匹配:

-

单位电容阵列

-

共同质心

-

屏蔽

-

信号走线:

-

差分对:平行,等长,对称

-

敏感节点:屏蔽,远离干扰源

-

电源线:宽线,多个通孔

-

时钟线:屏蔽,最小化耦合

电源分布:

-

电源环:芯片周围

-

电源条:内部供电

-

去耦电容:高频和低频

-

ESD保护:输入输出端

9.3 数字后端流程

综合(Synthesis):

RTL → 门级网表

优化:面积,时序,功耗

布局(Placement):

标准单元放置

目标:线长最小,时序满足

时钟树综合(CTS):

平衡时钟延迟

时钟偏差最小化

布线(Routing):

全局布线

详细布线

时序驱动布线

时序验证:

静态时序分析(STA)

建立时间,保持时间检查

物理验证:

DRC:设计规则检查

LVS:版图与原理图一致性检查

ERC:电气规则检查

天线检查

10.1 测试方法

模拟测试:

-

参数测试:DC参数,AC参数

-

功能测试:输入输出特性

-

结构测试:故障模型测试

-

内建自测试(BIST):片上测试电路

数字测试:

-

固定故障模型:stuck-at 0/1

-

故障覆盖率:检测到的故障比例

-

自动测试向量生成(ATPG)

-

扫描测试:扫描链插入

-

边界扫描(JTAG):IEEE 1149.1

混合信号测试:

-

DAC测试:INL,DNL

-

ADC测试:静态和动态参数

-

PLL测试:锁定时间,抖动

-

SerDes测试:眼图,误码率

10.2 可测性设计(DFT)

扫描设计:

-

扫描链插入

-

全扫描,部分扫描

-

测试压缩

-

测试点插入

内建自测试(BIST):

-

测试向量生成

-

输出响应分析

-

线性反馈移位寄存器(LFSR)

-

多输入特征寄存器(MISR)

边界扫描:

-

TAP控制器

-

指令寄存器

-

数据寄存器

-

测试访问端口

模拟DFT:

-

测试总线

-

测试点

-

内建自测试

-

数字辅助测试

11.1 低电压设计

亚阈值电路:

工作在亚阈值区,极低功耗

ID=I0e(VGS−VTH)/nVT(1−e−VDS/VT)

挑战:低速度,高工艺敏感性

近阈值计算:

在阈值电压附近工作

优点:能效高

挑战:高工艺变化敏感性,需要自适应设计

多电压域:

不同模块不同电压

电平转换器

电压岛隔离

动态电压频率调整(DVFS):

根据工作负载调整电压和频率

需要电压调节器和时钟产生电路

11.2 抗工艺变化设计

统计静态时序分析(SSTA):

考虑工艺变化的时序分析

用统计分布代替固定值

自适应体偏置(ABB):

根据工艺和温度调整体偏置

补偿阈值电压变化

可调电路:

可调电阻,电容,电流

修调技术:熔丝,反熔丝,EEPROM

容错设计:

冗余设计

错误检测与纠正(ECC)

自适应校准

11.3 3D集成电路

技术:

-

硅通孔(TSV)

-

微凸点

-

混合键合

优势:

-

减小互连长度

-

提高带宽

-

异质集成

挑战:

-

热管理

-

测试

-

设计工具

12.1 自顶向下设计

-

系统规格:功能,性能,功耗,成本

-

架构设计:算法,架构,模块划分

-

RTL设计:硬件描述语言(Verilog/VHDL)

-

验证:仿真,形式验证

-

综合:RTL → 门级网表

-

布局布线:物理设计

-

后仿真:带寄生参数仿真

-

流片:制造

-

测试:芯片测试

12.2 混合信号设计

协同设计:

-

模拟和数字协同设计

-

混合信号仿真

-

数模接口设计

混合信号仿真:

-

模拟用Spice

-

数字用Verilog/VHDL

-

混合仿真器

数模接口:

-

电平转换

-

同步

-

噪声隔离

12.3 设计验证

仿真验证:

-

功能仿真

-

时序仿真

-

功耗仿真

-

混合信号仿真

形式验证:

-

等价性检查

-

模型检查

-

定理证明

物理验证:

-

DRC

-

LVS

-

ERC

-

天线检查

13.1 运算放大器设计实例

规格:

-

增益:>80dB

-

单位增益带宽:>100MHz

-

相位裕度:>60°

-

转换速率:>50V/μs

-

输入共模范围:轨到轨

-

输出摆幅:轨到轨

-

功耗:<2mW

-

电源电压:1.8V

设计步骤:

-

选择架构:两级运放

-

第一级:折叠式共源共栅,高增益

-

第二级:共源级,大摆幅

-

频率补偿:米勒补偿+调零电阻

-

偏置电路:恒跨导偏置

-

共模反馈:稳定输出共模电平

-

仿真验证:DC,AC,瞬态,工艺角

-

版图设计:匹配,对称,屏蔽

设计计算:

-

增益要求:Av=gm1gm6(ro2∥ro4)(ro6∥ro7)>104

-

带宽要求:GBW=2πCCgm1>100MHz

-

转换速率:SR=CCI5>50V/μs

-

功耗:P=(I5+Ibias)VDD<2mW

-

从这些方程确定晶体管尺寸和偏置电流

13.2 低功耗SAR ADC设计实例

规格:

-

分辨率:10位

-

采样率:1MS/s

-

功耗:<100μW

-

电源电压:1.0V

-

输入范围:0-1.0V

-

无杂散动态范围(SFDR):>70dB

设计步骤:

-

架构:异步SAR ADC

-

采样保持:电荷重分布

-

电容DAC:二进制加权电容阵列

-

比较器:动态锁存比较器

-

SAR逻辑:异步控制

-

时序:内部时钟产生

-

校准:后台校准

电容DAC设计:

单位电容:Cu=22NVLSB2kT,考虑热噪声

总电容:Ctotal=2NCu

电容匹配:DNL < 0.5LSB → 匹配精度要求

比较器设计:

输入失调:< 0.5LSB

噪声:< 0.5LSB

速度:< 1/2 采样周期

功耗:最小化

时序设计:

采样相位

比较相位

DAC稳定时间

数字逻辑延迟

13.3 低噪声放大器设计实例

规格:

-

频率:2.4GHz

-

增益:>15dB

-

噪声系数:<2dB

-

输入匹配:S11 < -10dB

-

线性度:IIP3 > -10dBm

-

功耗:<5mW

-

电源电压:1.2V

设计步骤:

-

选择架构:源极负反馈LNA

-

输入匹配:Lg,Ls,C_gs谐振

-

晶体管尺寸:优化噪声和增益

-

输出匹配:最大化功率传输

-

偏置:电流源偏置

-

稳定性:确保无条件稳定

-

版图:对称,屏蔽,减小寄生

输入匹配:

从源阻抗Z_s匹配到晶体管输入:

Zin=jωLg+jωCgs1+ωTLs

其中ωT=gm/Cgs

匹配条件:Re(Z_in)=R_s,Im(Z_in)=0

噪声优化:

最优晶体管宽度:

Wopt=3ωLCoxRs1

最优噪声系数:

Fmin=1+2.4αγωTω

14.1 先进工艺挑战

FinFET/纳米线晶体管:

-

三维结构

-

量子效应

-

寄生参数

-

模型复杂性

变异增加:

-

随机掺杂波动

-

线边缘粗糙度

-

统计性更强

-

需要统计设计

互连挑战:

-

RC延迟

-

串扰

-

电迁移

-

3D集成

14.2 新计算范式

近似计算:

-

允许误差

-

降低功耗

-

应用:图像处理,机器学习

存内计算:

-

存储器中计算

-

减少数据移动

-

适合矩阵运算

神经形态计算:

-

模拟大脑

-

脉冲神经网络

-

低功耗,高能效

量子计算:

-

量子比特

-

量子门

-

错误校正

14.3 设计方法学

机器学习辅助设计:

-

电路优化

-

版图生成

-

测试向量生成

-

良率预测

高层次综合:

-

从算法到RTL

-

自动优化

-

缩短设计周期

开源EDA:

-

开源工具

-

降低设计成本

-

社区合作

电路设计实现理论是一个涵盖从器件物理到系统集成的广泛领域。随着工艺进步和系统复杂度的增加,电路设计需要综合考虑性能、功耗、面积、成本、可靠性、可制造性等多个方面。未来的电路设计将更加依赖于:

-

跨层次优化:从系统级到器件级的协同优化

-

智能化设计:机器学习辅助的自动设计

-

可靠设计:考虑老化、变异、可靠性

-

安全设计:硬件安全,防侧信道攻击

-

可持续设计:低功耗,环保材料

电路设计既是科学也是艺术,需要深厚的理论基础、丰富的实践经验和创新的设计思维。随着新技术和新应用的不断涌现,电路设计理论也将持续发展和完善。

1.1 计算范式的根本性转变

传统冯·诺依曼架构的瓶颈:

-

内存墙:数据在处理器和存储器之间的频繁搬运

-

功耗墙:数据移动能耗远高于计算能耗

Eaccess≈640pJ(片外DRAM访问)

Ecompute≈1pJ(32位浮点运算)

-

带宽限制:总线带宽成为性能瓶颈

存内计算的核心思想:

将计算单元与存储单元深度融合,实现"数据不动、计算主动"的新范式:

计算位置=f(数据位置)

而不是传统架构的:

数据移动=g(计算位置)

1.2 物理基础与实现原理

物理实现的三个层次:

-

器件级:利用存储器的物理特性直接进行计算

-

电阻型存储器:欧姆定律 I=V/R

-

电荷型存储器:电容电荷共享 Q=CV

-

磁存储器:自旋输运特性

-

-

电路级:通过模拟电路实现计算功能

-

模拟乘加运算:基尔霍夫电流定律

-

矩阵运算:跨导阵列

-

逻辑运算:忆阻器逻辑

-

-

架构级:新型计算架构

-

近内存计算

-

存内计算

-

存算一体

-

数学表达:

对于矩阵-向量乘法 y=Wx:

传统架构:

yi=j=1∑NWij⋅xj需要N次访存

存内计算:

yi=fI−V(j=1∑NGij⋅Vj)在存储位置完成

其中 Gij是电导值,对应权重 Wij

2.1 数字存内计算

基于SRAM的计算:

-

6T/8T-SRAM计算:在存储阵列中集成计算逻辑

-

位线计算:利用位线进行多输入逻辑运算

-

计算模式:

-

布尔逻辑运算

-

多位数加法

-

查找表操作

-

SRAM存内计算电路示例:

6T SRAM单元的计算能力扩展:

-

标准读取:差分位线

-

计算模式:多行同时激活

-

模拟域计算:电荷共享

-

数字域计算:位线逻辑

计算原理:

对于N个输入的行波进位加法:

计算步骤:

1. 预充电位线

2. 同时激活多行

3. 位线电压表示部分和

4. 感应放大器检测结果

性能特点:

-

精度:数字精度,无模拟误差

-

速度:接近SRAM读取速度

-

能效:中等,比模拟高

-

适用场景:高精度,低并行度计算

2.2 模拟存内计算

基于非易失存储器的计算:

1. 忆阻器(ReRAM/Memristor)阵列:

物理原理:I=G(V)⋅V,其中电导G可编程

矩阵乘法实现:

Ii=j=1∑NGijVj

对应:

yi=j=1∑NWijxj

2. 相变存储器(PCM):

电阻状态:晶态(低阻)vs 非晶态(高阻)

电导可连续调节

3. 磁阻存储器(MRAM/STT-MRAM):

电阻状态:平行(低阻)vs 反平行(高阻)

读写速度快,耐久性高

4. 闪存(Flash)计算:

利用浮栅晶体管阈值电压可调特性

多级单元(MLC)实现多比特存储

模拟计算电路架构:

1. 1T1R阵列结构:

-

晶体管:选择控制

-

忆阻器:存储权重

-

输入:字线电压

-

输出:位线电流

2. 计算过程:

输入向量 → 电压脉冲 → 电流累加 → ADC转换 → 输出

3. 偏置方案:

-

电压偏置:V=Vread⋅x

-

时间偏置:脉冲宽度调制

-

频率偏置:脉冲频率调制

2.3 混合模式存内计算

数模混合计算:

-

模拟域:高并行矩阵运算

-

数字域:非线性激活、规约操作

-

模数转换:模拟结果数字化

存内-近内存混合:

-

存内:密集矩阵运算

-

近内存:控制逻辑、不规则计算

-

通过高带宽互连连接

3.1 矩阵-向量乘法(MVM)

模拟实现原理:

对于M×N矩阵W和N维向量x:

-

矩阵W映射到电导阵列G

-

向量x编码为输入电压V

-

输出电流I = G·V

-

通过基尔霍夫电流定律实现累加

电路实现:

列方向:电流累加

I_j = Σ_i (G_ij * V_i)

行方向:电压输入

精度分析:

总谐波失真:

THD=10log10(P1∑n=2∞Pn)

其中P_n是n次谐波功率

非理想因素:

-

电导值量化误差

-

线电阻压降

-

晶体管非理想性

-

ADC量化噪声

3.2 卷积计算

存内卷积实现:

-

权重固定:卷积核映射到存储阵列

-

输入滑动:通过多路复用实现滑动窗口

-

并行计算:多个卷积窗口同时计算

Toeplitz矩阵转换:

将卷积转换为矩阵乘法:

y=Wtoeplitz⋅xim2col

其中W_{toeplitz}是循环矩阵

数据流优化:

-

输入重用:减少数据移动

-

输出累加:部分和累加

-

脉动阵列:流水线计算

3.3 注意力机制计算

自注意力实现:

Attention(Q,K,V)=softmax(dkQKT)V

存内计算分解:

-

QK^T:矩阵乘法,存内计算

-

缩放除法:数字电路

-

Softmax:混合实现

-

乘以V:矩阵乘法,存内计算

多头注意力:

并行计算多个头的注意力

硬件复用,权重重新配置

4.1 非易失存储器件

忆阻器(ReRAM):

物理机制:

-

电化学金属化(ECM):金属细丝形成/断裂

-

价态变化(VCM):氧空位迁移

-

热化学(TCM):相变

特性参数:

-

阻值范围:1kΩ-1MΩ

-

开关比:10-1000

-

耐久性:10^6-10^12次

-

保持时间:>10年

-

开关速度:ns-μs

-

操作电压:<3V

电导调节:

SET过程:电压脉冲 → 电导增加

RESET过程:反向电压 → 电导减小

多级存储:通过脉冲控制电导值

相变存储器(PCM):

物理机制:

-

晶态:低阻,有序结构

-

非晶态:高阻,无序结构

-

通过加热和淬火转换

特性:

-

阻值比:10^2-10^6

-

耐久性:10^8-10^9次

-

保持时间:>10年

-

多级:2-4bits/单元

自旋转移矩磁阻存储器(STT-MRAM):

物理机制:

-

自旋极化电流改变磁化方向

-

隧道磁阻效应(TMR)

特性:

-

开关速度:<10ns

-

耐久性:>10^15次

-

保持时间:>10年

-

操作电压:~1V

铁电存储器(FeRAM/FeFET):

物理机制:

-

铁电极化翻转

-

剩余极化存储信息

特性:

-

开关速度:~ns

-

耐久性:10^10-10^12次

-

多级:通过部分极化实现

4.2 易失存储器件

静态随机存储器(SRAM):

计算增强型SRAM:

-

8T-SRAM:双端口,支持并行读取

-

10T-SRAM:增强计算能力

-

差分计算:利用差分位线

计算模式:

-

多行激活

-

模拟计算模式

-

数字逻辑模式

动态随机存储器(DRAM):

计算DRAM:

-

利用电容电荷共享

-

行缓冲计算

-

批量位操作

限制:

-

刷新开销

-

精度有限

-

访问冲突

4.3 新型存储器件

铁电场效应晶体管(FeFET):

-

非易失性

-

逻辑兼容

-

多级存储

-

低功耗操作

赛道存储器(Racetrack Memory):

-

磁畴壁移动

-

高密度

-

快速访问

自旋轨道矩存储器(SOT-MRAM):

-

读写分离

-

高速度

-

高耐久性

原子开关:

-

原子尺度

-

量子效应

-

超低功耗

5.1 模拟存内计算电路

交叉阵列设计:

基本结构:

M×N交叉阵列

-

行:输入线

-

列:输出线

-

交叉点:存储单元

电导映射:

权重W_ij映射为电导G_ij:

Gij=Gmin+Wmax−WminWij−Wmin⋅(Gmax−Gmin)

偏置电路:

输入编码:

-

电压幅度调制:Vi=αxi

-

脉冲宽度调制:脉宽∝x_i

-

脉冲频率调制:频率∝x_i

读出电路:

跨阻放大器:

Vout=−Rf⋅Iin

设计考虑:带宽,噪声,线性度

电流镜积分:

Iout=βIin,Vout=C1∫Ioutdt

模数转换器(ADC):

需求:

-

中低分辨率:4-8位

-

高能量效率:<100fJ/转换步

-

小面积

-

并行操作

ADC架构:

-

逐次逼近型(SAR ADC):

-

中等精度

-

低功耗

-

面积小

-

速度中等

-

-

单斜率ADC:

-

结构简单

-

高线性度

-

速度慢

-

适合列并行

-

-

Flash ADC:

-

速度快